ZHCABI1B February 2022 – January 2024 AM2434 , AM6411 , AM6412 , AM6421 , AM6441 , AM6442

4.3.1 测试设置

AM64x-PCIE 基准测试设置

下面是我们对 PCIE-BCDMA-DDR 读取性能(就带宽而言)进行基准测试所用的设置。

硬件详细信息:

- TMDS64EVM

- PCIE 电缆可从 Adex Electronics 获得。

有关详细信息,请参阅:

软件详细信息:- 测试代码可从 GitHub 链接获取,该代码以 MCU+ SDK 8.6 为基准。

注: 默认情况下,在 MCU+ SDK 中,最多可以将 4 个 UDMA 通道分配给 R5F_0_0 内核。

如果要运行测试的通道数超过默认配置,您需要首先使用资源管理 (RM) 工具来管理内核的 UDMA 通道分配。

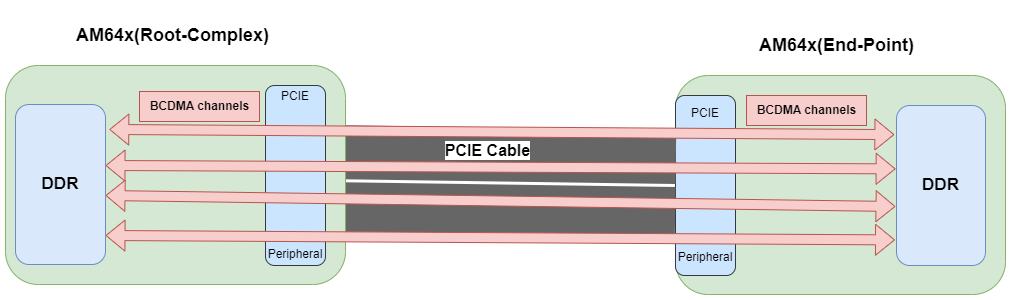

图 4-2 AM64x-PCIE 基准测试设置

图 4-2 AM64x-PCIE 基准测试设置 图 4-3 AM64x(PCIE 基准测试)数据流. 以下是 PCIE 基准测试期间 2-AM64x 电路板之间数据流的详细信息。

图 4-3 AM64x(PCIE 基准测试)数据流. 以下是 PCIE 基准测试期间 2-AM64x 电路板之间数据流的详细信息。EP 在 PCIE 中设置缓冲区,RC 将读取它并将其复制到 DDR 中

例如,在 RC 侧:

PCIE_loc_1 = 0x68000000UL + 0x00000000U

PCIE_loc_2 = 0x68000000UL + 0x01000000U

PCIE_loc_3 = 0x68000000UL + 0x02000000U

PCIE_loc_4 = 0x68000000UL + 0x03000000U

和

DDR_loc_1 = 0xA0000000 + 0x00000000U

DDR_loc_2 = 0xA0000000 + 0x01000000U

DDR_loc_3 = 0xA0000000 + 0x02000000U

DDR_loc_4 = 0xA0000000 + 0x03000000U

以此类推。