ZHCA963 August 2019 TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28374D , TMS320F28375D , TMS320F28376D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28378D , TMS320F28379D , TMS320F28379D-Q1

6 生成 PWM 信号

CLB 可以使用自己的可配置块来生成 PWM 波形。假设需要在系统的状态为正在打开或正在关闭时生成 PWM 信号。对于此系统,来自 CLB 逻辑块的两个 PWM 信号分别是:

- 正在打开状态:第一个 PWM 信号有效,并具有可修改的周期和占空比,而第二个 PWM 信号保持低电平。

- 正在关闭状态:第一个 PWM 信号保持低电平,而第二个 LOW 信号有效并具有可修改的周期和占空比。

FSM0、FSM2 和 COUNTER1 生成 PWM 信号。计数器子模块用作 PWM 的主要部分,FSM0 和 FSM2 则构成逻辑的剩余部分。需要这些角色才能生成 PWM 波形。

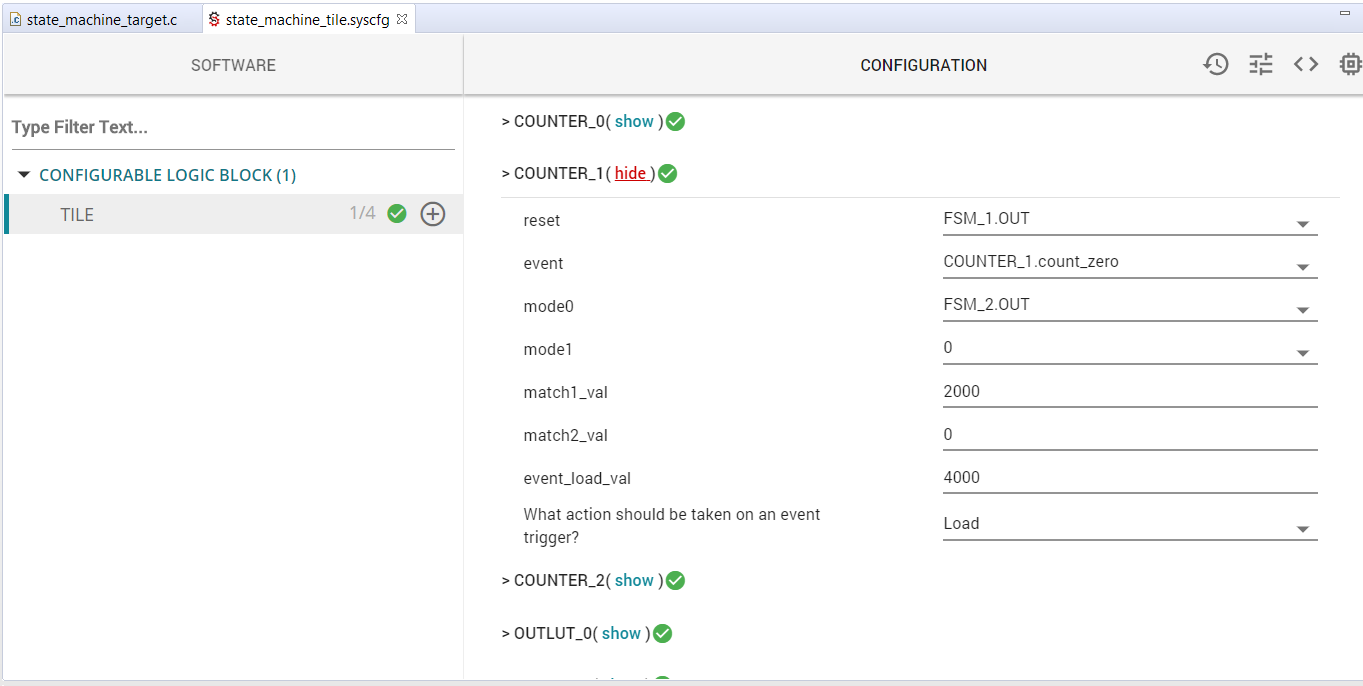

将 COUNTER1 设置为在倒计数模式下运行,并在计数器达到 ZERO 或指定的匹配值时生成信号。以下各项总结了对 COUNTER1 的要求:

- 从 load_val (mode1 = 0) 倒计数。

- 当发生 counter=ZERO 事件时,将 load_val 加载到计数器中。

- 使用 COUNTER1 的 load_val 寄存器设置 PWM 信号的周期。

- 在后续步骤中使用在 counter=match1_val 时生成的事件。

- 使用 COUNTER1 的 match1_val 寄存器设置 PWM 的占空比。

- 计数器的启用信号是 mode0。此信号应当只在系统处于正在打开或正在关闭状态时有效(此信号将在后续步骤中创建,做为计数器的输入信号)。

- 当检测到状态转换为正在打开或正在关闭状态时,重置计时器(已经可以从 FSM1 输出获得此信号)。

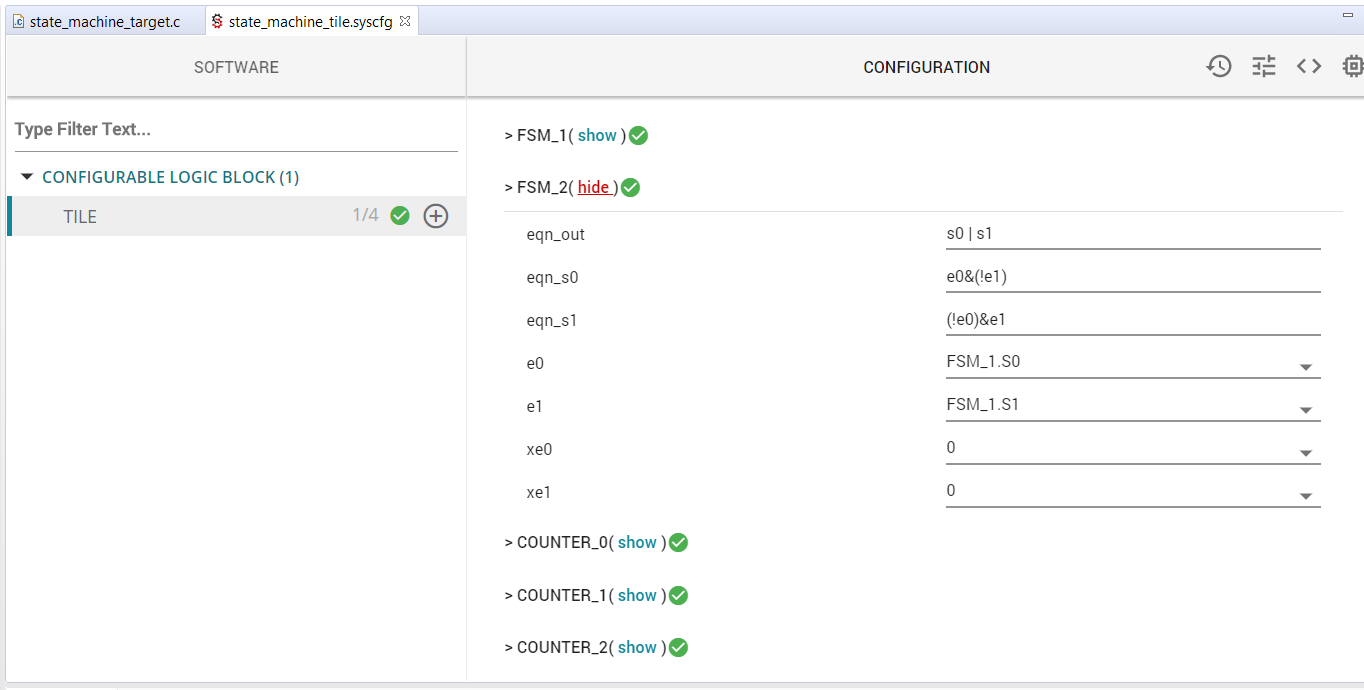

这样就设置了基于时间的 PWM 计数器。接下来,创建只在系统处于正在打开或正在关闭状态时有效的信号。要创建此信号,需要将 FSM2 用作 3 输出 LUT 而非有限状态机。设置 FSM2 以满足以下要求:

- S0:只在正在打开状态激活时有效

- S1:只在正在关闭状态激活时有效

- 输出:在正在关闭或正在打开状态激活时有效

将来自 FSM2 的输出用作 COUNTER1 mode0 的输入。COUNTER1 的 Mode0 只在系统处于正在关闭或正在打开状态时有效。

Figure 8 和Figure 9 显示了 FSM2 和 COUNTER1 的 SysConfig 配置。

Figure 8. FSM2 配置

Figure 8. FSM2 配置  Figure 9. COUNTER1 配置

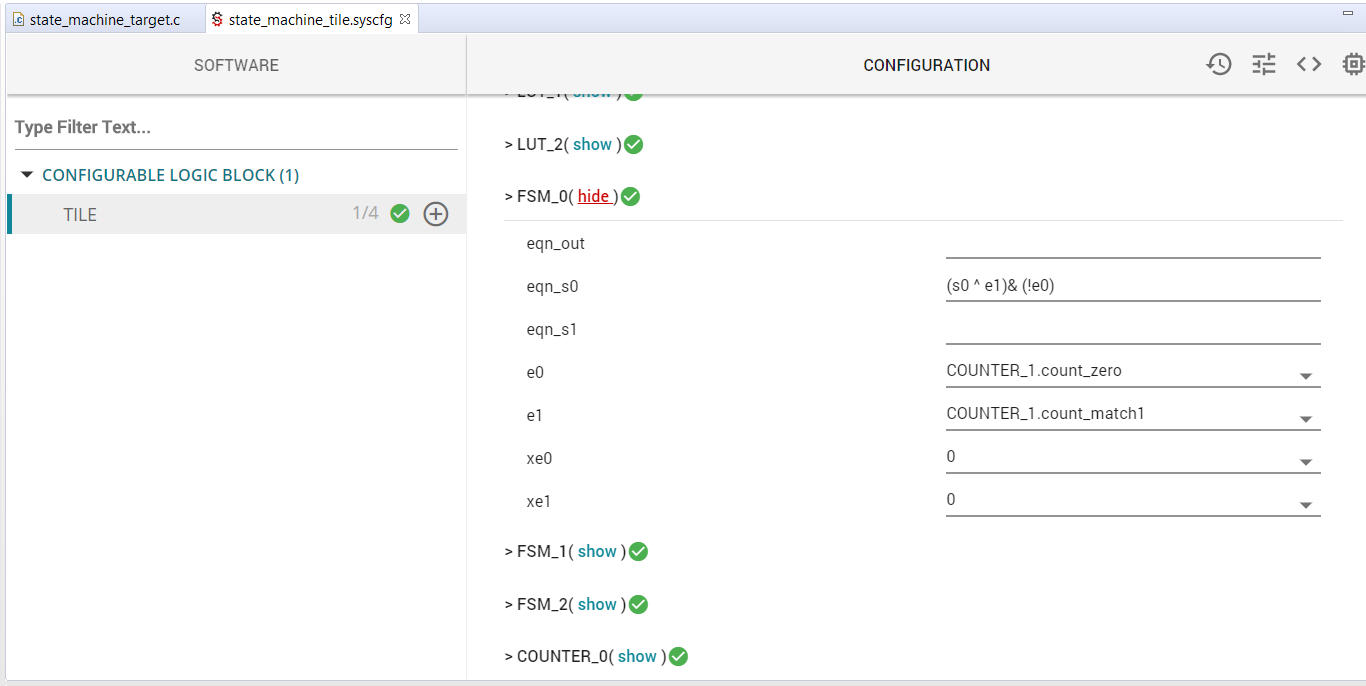

Figure 9. COUNTER1 配置 创建 PWM 信号的最后一步是使用 FSM 模块,根据 COUNTER1 和 FSM2 生成的事件和信号生成 PWM 波形。使用 FSM0 s0 生成 PWM 信号。当 COUNTER1 发生 counter=ZERO 事件时,s0 必须清除为低电平。当 COUNTER1 发生 counter=match1_val 事件时,s0 必须设置为高电平。

Figure 10 显示了 FSM0 的 SysConfig 配置。

Figure 10. FSM0 配置

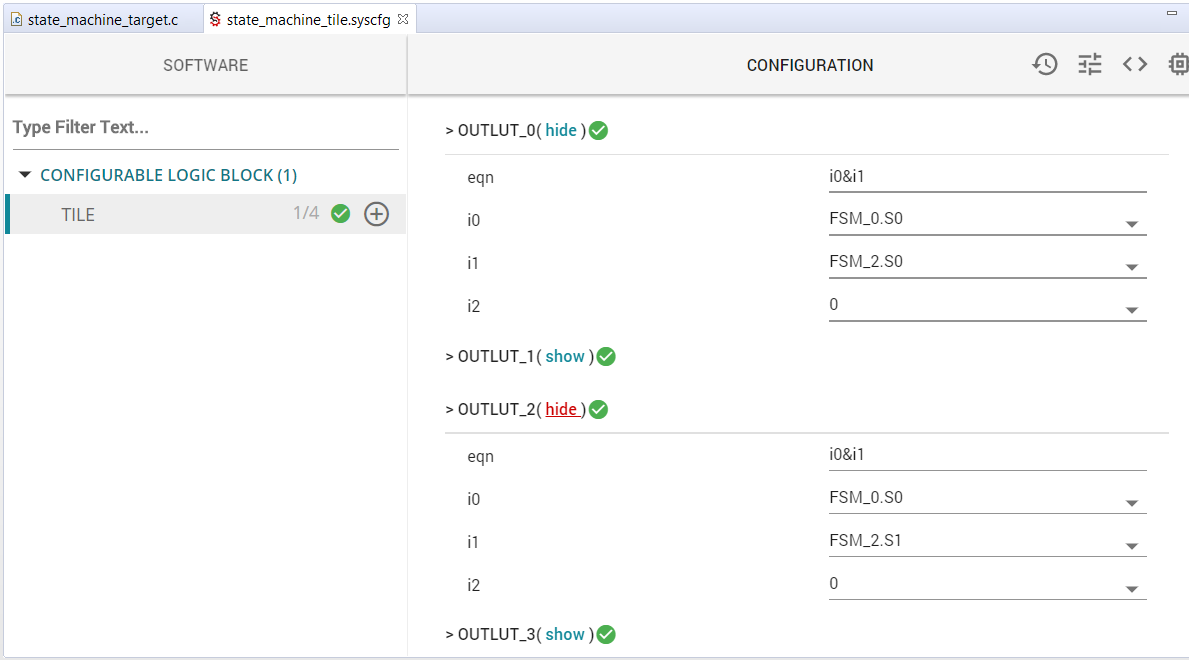

Figure 10. FSM0 配置 最后,将 PWM 信号拆分为两个信号:一个用于正在关闭状态,一个用于正在打开状态。OUTLUT0 和 OUTLUT2 输出这两个信号。当系统处于正在打开状态时,OUTLUT0 将输出 PWM 信号,OUTLUT2 将保持低电平。当系统处于正在关闭状态时,OUTLUT2 将输出 PWM 信号,OUTLUT0 将保持低电平。Figure 11 显示了 OUTLUT0 和 OUTLUT2 的 SysConfig 配置。

Figure 11. OUTLUT0 和 OUTLUT2 配置

Figure 11. OUTLUT0 和 OUTLUT2 配置 在下一步,可以在运行期间随时使用 C28x 内核和 HLC 子模块来更新 PWM 周期和占空比。