ZHCA963 August 2019 TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28374D , TMS320F28375D , TMS320F28376D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28378D , TMS320F28379D , TMS320F28379D-Q1

8 已完成的设计

Figure 14 显示了此设计的整个方框图。您可以利用各个子模块之间的关系了解 CLB 逻辑块要实现的整体目标。

Figure 14. 已完成的设计方框图

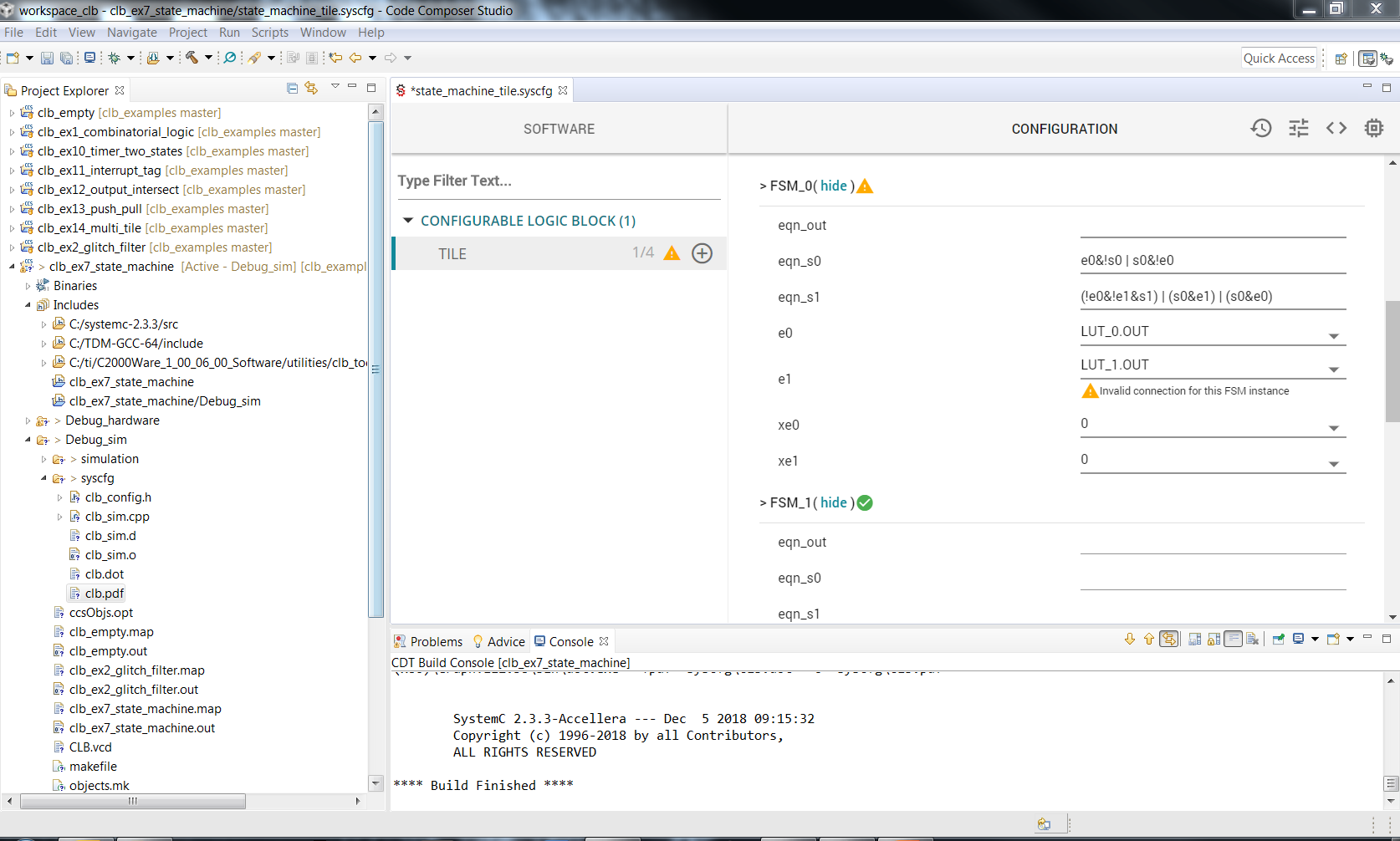

选择要使用的子模块时要小心谨慎。例如,上述设计无法使用 FSM0 来取代 FSM1,原因在于硬件限制不允许选择 LUT1 输出作为 FSM0 e1 的输入。这是一个无效配置的示例。《TMS320F2837xD 双核 Delfino™ 微控制器技术参考手册》 显示了这些无效设置的完整列表。硬件中的几组输入已经断开,以免形成逻辑环路。Figure 15 显示了 CLB SysConfig 工具为了向用户通报此设计错误而生成的警告。

Figure 15. 此示例的无效连接

Figure 15. 此示例的无效连接