ZHCA963 August 2019 TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28374D , TMS320F28375D , TMS320F28376D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28378D , TMS320F28379D , TMS320F28379D-Q1

4 对输入采样

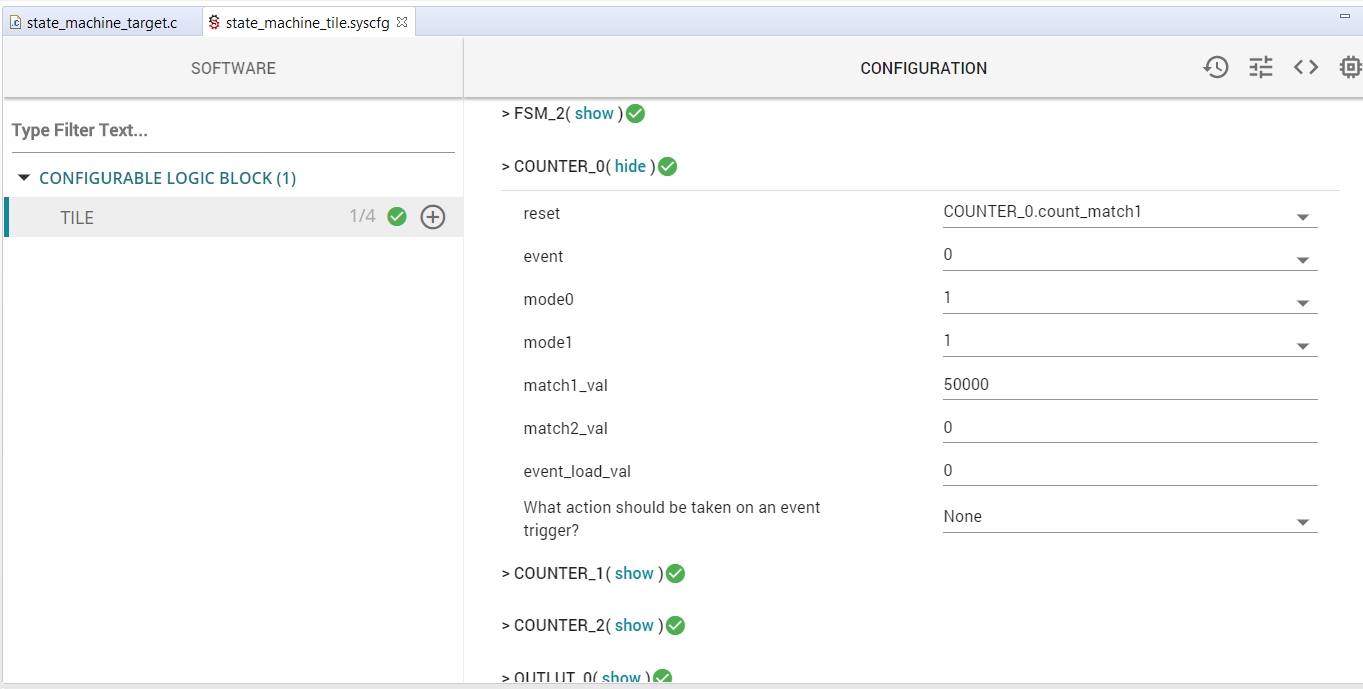

设计这个特定系统的第一步是对外部输入进行采样,以便对最终的设计进行测试。我们将使用计数器每 50000 个时钟周期对 BOUNDARY IN0 和 IN1 进行一次采样,而不是将来自 GPIO 的源输入用作 BOUNDARY IN0 和 IN1。使用示波器显示正在关闭与正在打开状态之间的转换,以便于查看轮询结果。Section 10 显示了这种情况。

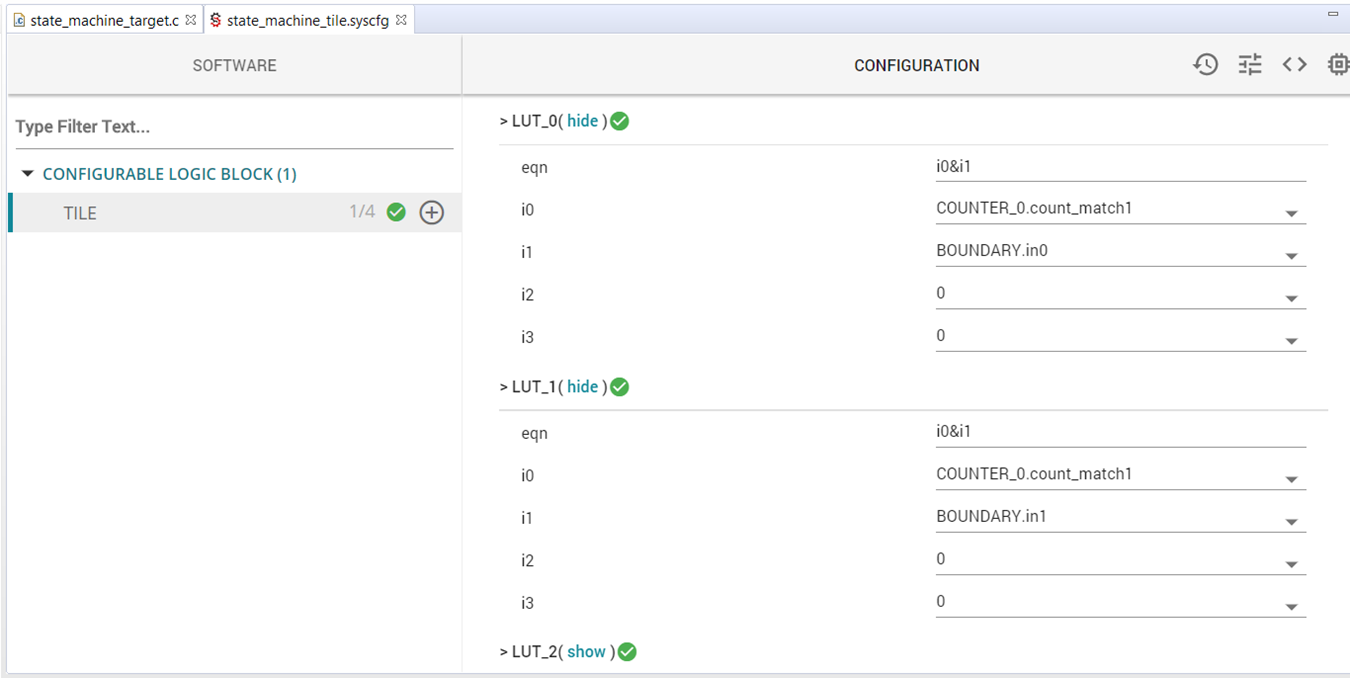

将计数器模块 (COUNTER0) 与 LUT0 和 LUT1 配合使用,以生成采样输入信号,供 FSM 子模块随后使用。采样逻辑的要求如下所示:

- 使用 COUNTER0 每 50000 个时钟周期生成一个信号 (match1_val = 50000)

- 始终启用计数器 (mode0 = 1) 并进行计数 (mode1 = 1)

- 在发生 MATCH1 事件时重置计数器

- 使用 LUT0 和 LUT1

- 将两个输入信号(BOUNDARY IN0 和 IN1)与 COUNTER0 MATCH1 事件信号配合使用,以生成采样输入信号,供 FSM 随后使用

Figure 2 和Figure 3 显示了这些要求以及如何在示例项目的 SysConfig 设置中使用这些要求。

Figure 2. COUNTER0 配置

Figure 2. COUNTER0 配置  Figure 3. LUT0 和 LUT1 配置

Figure 3. LUT0 和 LUT1 配置