SBVA100 December 2022 LP2992 , TPS786 , TPS7A30 , TPS7A3001-EP , TPS7A33 , TPS7A39 , TPS7A4501-SP , TPS7A47 , TPS7A47-Q1 , TPS7A4701-EP , TPS7A49 , TPS7A52 , TPS7A52-Q1 , TPS7A53 , TPS7A53-Q1 , TPS7A53A-Q1 , TPS7A53B , TPS7A54 , TPS7A54-Q1 , TPS7A57 , TPS7A7100 , TPS7A7200 , TPS7A7300 , TPS7A80 , TPS7A8300 , TPS7A83A , TPS7A84 , TPS7A84A , TPS7A85 , TPS7A85A , TPS7A87 , TPS7A89 , TPS7A90 , TPS7A91 , TPS7A92 , TPS7A94 , TPS7A96 , TPS7B7702-Q1 , TPS7H1111-SEP , TPS7H1111-SP , TPS7H1210-SEP

4.2 TPS7A47xx

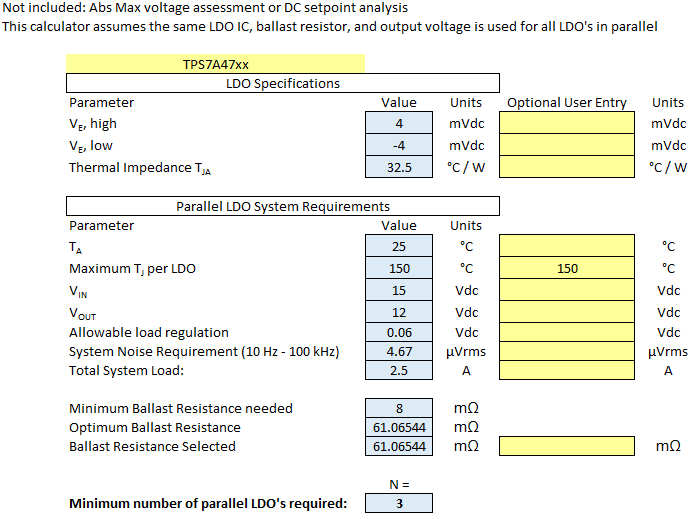

Consider the following system power requirements: VIN = 15 V, VOUT = 12 V, and ILOAD = 2.5 A. The system noise requirement is 4.67 uVRMS, we need the PSRR to be at least 50 dB at 1 MHz, and the additional load regulation can be as high as 60 mV. The application requires high reliability and may operate above 125 C in the future, so an extended performance (-EP) device with an operating junction temperature of 150 C is desired. We select the TPS7A47 LDO to be paralleled to meet the mid Vin, high reliability and increased thermal specifications. We enter these system requirements into the system architecture calculator [see reference 5]. As shown in Figure 4-2 we need at least 3 parallel TPS7A47 LDOs to meet these system requirements.

These results do not include PSRR, which must be assessed separately. A review of the TPS7A47 data sheet reveals plenty of margin in the PSRR curves to the system 50 dB requirement at 1 MHz. Thus the PSRR specification will not change the results in Figure 4-2. If desired, a statistical analysis on VLOAD and IOUTn can be completed as discussed in Section 3.

Figure 4-2 Parallel LDO System Requirement

Analysis using the TPS7A47 LDO

Figure 4-2 Parallel LDO System Requirement

Analysis using the TPS7A47 LDO