KOKA018B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

2.1 디지털 전원 공급 장치

VCORE 레귤레이터

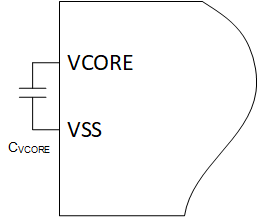

내부 저손실 선형 전압 레귤레이터가 장치 코어에 전력을 공급하기 위해 1.35V 공급 레일을 생성합니다. 일반적으로 코어 레귤레이터 출력(VCORE)은 CPU, 디지털 주변 장치 및 장치 메모리를 비롯한 코어 로직에 전원을 공급합니다. 코어 레귤레이터에는 장치 VCORE 핀과 VSS(접지) 사이에 연결된 외부 커패시터(CVCORE)가 필요합니다(그림 2-1 참조). CVCORE의 올바른 값과 허용 오차는 장치별 데이터 시트를 참조하십시오. CVCORE는 VCORE 핀 가까이에 배치해야 합니다.

코어 레귤레이터는 종료를 제외한 모든 전원 모드에서 활성화됩니다. 다른 모든 전원 모드(실행, 절전, 정지 및 대기)에서 레귤레이터의 구동 강도는 각 모드의 최대 부하 전류를 지원하도록 자동으로 구성됩니다. 이는 저전력 모드를 사용할 때 레귤레이터의 정동작 전류를 줄여서 저전력 성능을 향상시킵니다.

그림 2-1 VCORE 레귤레이터 회로

그림 2-1 VCORE 레귤레이터 회로