KOKA018B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

4.3 외부 클록 출력(CLK_OUT)

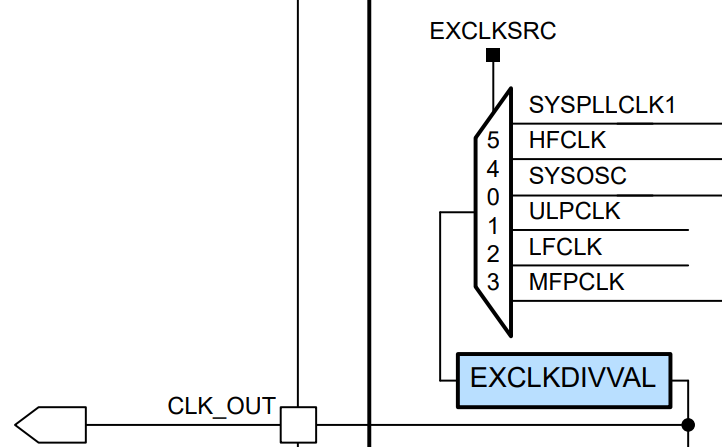

클록 출력 장치는 장치에서 외부 회로 또는 주파수 클록 카운터로 디지털 클록을 보낼 수 있습니다. 이 기능은 자체 클록 소스가 없는 외부 ADC와 같은 외부 회로를 클로킹하는 데 유용합니다. 클록 출력 장치에는 선택할 수 있는 유연한 소스 세트가 있으며, 여기에는 프로그래머블 디바이더가 포함되어 있습니다.

그림 4-6 MSPM0G 외부 클록 출력(CLK_OUT)

그림 4-6 MSPM0G 외부 클록 출력(CLK_OUT)CLK_OUT에 사용 가능한 클록 소스:

- SYSPLLCLK1

- HFCLK

- SYSOSC

- ULPCLK

- MFCLK

- LFCLK

선택한 클록 소스는 핀 또는 주파수 클록 카운터로 출력되기 전에 1, 2, 4, 8, 16, 32, 64 또는 128로 나눌 수 있습니다.