KOKA018B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

6.1 ADC 설계 고려 사항

MSPM0G 장치에는 12비트, 최대 4Msps, ADC(아날로그-디지털 컨버터)가 있습니다. ADC는 고속 12비트, 10비트 및 8비트 아날로그-디지털 변환을 지원합니다. ADC는 12비트 SAR 코어, 샘플/변환 모드 제어 및 최대 12개의 독립 변환 및 제어 버퍼를 구현합니다.

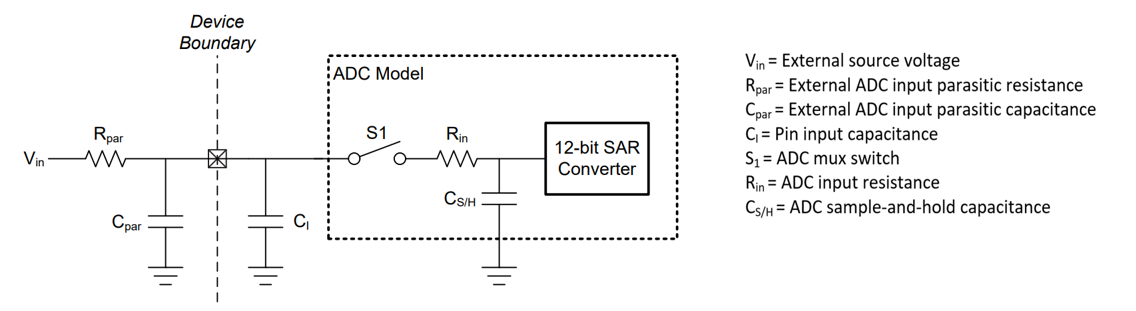

그림 6-1 ADC 입력 네트워크

그림 6-1 ADC 입력 네트워크원하는 변환 속도를 달성하고 높은 정확도를 유지하려면 하드웨어 설계에서 적절한 샘플링 시간을 보장해야 합니다. 샘플링(샘플 앤 홀드) 시간은 디지털 변환 전에 신호를 샘플링하는 시간을 결정합니다. 샘플 시간 동안 내부 스위치를 사용하여 입력 커패시터를 충전할 수 있습니다. 커패시터를 완전히 충전하는 데 필요한 시간은 ADC 입력 핀에 연결된 외부 AFE(아날로그 프런트 엔드)에 따라 달라집니다. 그림 6-1에서는 MSPM0G MCU의 일반적인 ADC 모델을 보여줍니다. Rin 및 CS/H 값은 장치별 데이터 시트에서 얻을 수 있습니다. AFE 구동 기능을 이해하고 신호를 샘플링하는 데 필요한 최소 샘플링 시간을 계산하는 것이 중요합니다. RPar 및 Rin 저항은 tsample에 영향을 미칩니다. 방정식 1은(는) n-비트 변환에 대한 최소 샘플 시간 tsample의 보수적 값을 계산하는 데 사용할 수 있습니다.

TI는 연속 고속(4Msps) ADC 성능을 평가하기 위해 충분한 신호 소스 드라이브 기능을 보장할 수 있도록 외부 버퍼를 추가할 것을 권장합니다. 설계 레퍼런스용으로, 권장 외부 OPA가 포함된 LP-MSPM0G3507 하드웨어 설계를 참조하십시오.