KOKA018B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

10.2.2 하드웨어 호출

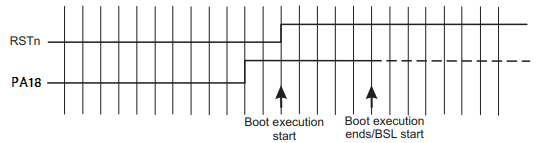

부트로더는 GPIO를 사용하여 BOOTRST 이후의 하드웨어 호출을 지원합니다. NONMAIN 플래시 메모리의 BSL 구성에는 GPIO 호출에 대한 패드, 핀 및 극성 정의가 포함되어 있습니다. 장치는 TI에서 특정 GPIO 및 극성에 맞게 구성되지만 소프트웨어는 NONMAIN 플래시 메모리의 BSL 구성에서 GPIO 핀 구성을 수정하여 이 기본값을 변경할 수 있습니다. 기본 BSL 호출 GPIO를 확인하려면 장치별 데이터 시트를 참조하십시오. 그림 10-1에서는 높은 수준에서 부트로더를 트리거할 수 있는 GPIO 핀 PA18의 예를 보여줍니다.

그림 10-1 구성된 GPIO 핀에서의 BSL 입력 시퀀스

그림 10-1 구성된 GPIO 핀에서의 BSL 입력 시퀀스