KOKA018B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

6.3 DAC 설계 고려 사항

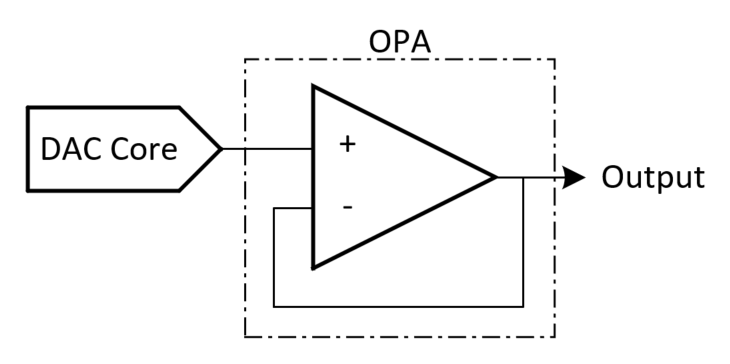

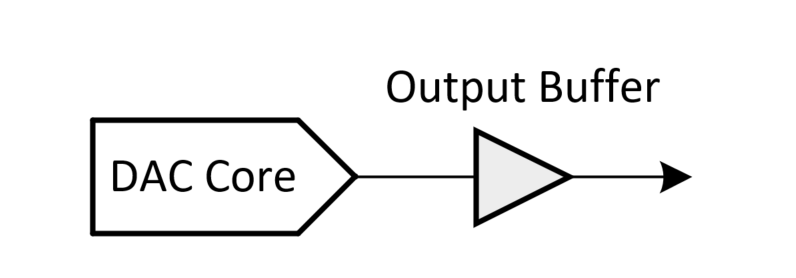

MSPM0G 장치에는 DAC 모듈 2개(8비트와 12비트)가 포함되어 있습니다. DAC는 레퍼런스 전압으로 사용할 수 있으며, OPA와 함께 작동하여 출력 패드를 직접 구동할 수도 있습니다. 12비트 DAC 모듈에는 버퍼가 포함되어 있으므로 패드로 직접 출력할 수 있습니다. 그러나 8비트 DAC 모듈은 일반적으로 OPA 및 COMP의 내부 기준 전압으로 사용되므로 외부 핀으로 출력하려면 드라이브 강도를 향상시키기 위해 OPA를 버퍼 모드로 구성해야 합니다.

모든 장치에 이러한 DAC 모듈 두 가지가 포함되어 있는 것은 아닙니다. 자세한 내용은 제품별 데이터 시트를 참조하십시오.

그림 6-4 8비트 DAC 블록 다이어그램

그림 6-4 8비트 DAC 블록 다이어그램 그림 6-5 8비트 DAC 및 OPA 출력 블록 다이어그램

그림 6-5 8비트 DAC 및 OPA 출력 블록 다이어그램 그림 6-6 12비트 DAC 출력 블록 다이어그램

그림 6-6 12비트 DAC 출력 블록 다이어그램