ZHCSBY9G July 2013 – June 2021 TPS54561

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Fixed Frequency PWM Control

- 7.3.2 Slope Compensation Output Current

- 7.3.3 Pulse Skip Eco-mode

- 7.3.4 Low Dropout Operation and Bootstrap Voltage (BOOT)

- 7.3.5 Error Amplifier

- 7.3.6 Adjusting the Output Voltage

- 7.3.7 Enable and Adjusting Undervoltage Lockout

- 7.3.8 Soft Start/Tracking Pin (SS/TR)

- 7.3.9 Sequencing

- 7.3.10 Constant Switching Frequency and Timing Resistor (RT/CLK) Pin)

- 7.3.11 Maximum Switching Frequency

- 7.3.12 Synchronization to RT/CLK Pin

- 7.3.13 Accurate Current Limit Operation

- 7.3.14 Power Good (PWRGD Pin)

- 7.3.15 Overvoltage Protection

- 7.3.16 Thermal Shutdown

- 7.3.17 Small Signal Model for Loop Response

- 7.3.18 Simple Small Signal Model for Peak Current Mode Control

- 7.3.19 Small Signal Model for Frequency Compensation

- 7.4 Device Functional Modes

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1

Buck Converter for 7-V to 60-V Input to 5-V at 5-A Output

- 8.2.1.1 Design Requirements

- 8.2.1.2

Detailed Design Procedure

- 8.2.1.2.1 Custom Design with WEBENCH® Tools

- 8.2.1.2.2 Selecting the Switching Frequency

- 8.2.1.2.3 Output Inductor Selection (LO)

- 8.2.1.2.4 Output Capacitor

- 8.2.1.2.5 Catch Diode

- 8.2.1.2.6 Input Capacitor

- 8.2.1.2.7 Slow Start Capacitor

- 8.2.1.2.8 Bootstrap Capacitor Selection

- 8.2.1.2.9 Undervoltage Lockout Set Point

- 8.2.1.2.10 Output Voltage and Feedback Resistors Selection

- 8.2.1.2.11 Compensation

- 8.2.1.2.12 Power Dissipation Estimate

- 8.2.1.2.13 Safe Operating Area

- 8.2.1.2.14 Discontinuous Conduction Mode and Eco-mode Boundary

- 8.2.1.3 Application Curves

- 8.2.2 Inverting Buck-Boost Topology for Positive Input to Negative Output

- 8.2.3 Split-Rail Topology for Positive Input to Negative and Positive Output

- 8.2.1

Buck Converter for 7-V to 60-V Input to 5-V at 5-A Output

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 说明

TPS54561 是一款具有集成式高侧 MOSFET 的 60V、5A、降压稳压器。按照 ISO 7637 标准,此器件能够耐受的负载突降脉冲高达 65V。它采用电流模式控制,可实现简单的外部补偿和灵活的组件选择。一个低纹波脉冲跳跃模式将无负载时的电源电流减小至 152μA。当使能引脚被拉至低电平时,关断电源电流被减少至 2μA。

欠压闭锁在内部设定为 4.3V,但可用使能引脚上的一个外部电阻分压器将之提高。输出电压启动斜坡由软启动引脚控制,该引脚还可被配置用来控制时序/跟踪。开漏电源正常信号表示输出处于其标称电压的 93% 至 106% 之间。

宽可调开关频率范围可针对效率或者外部组件尺寸进行优化。逐周期电流限制、频率折返和热关断在过载条件下保护内部和外部组件。

TPS54561 采用 10 引脚 4mm × 4mm WSON 封装。

器件信息

| 器件型号 | 封装(1) | 封装尺寸(标称值) |

|---|---|---|

| TPS54561 | WSON (10) | 4.00mm × 4.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

简化原理图

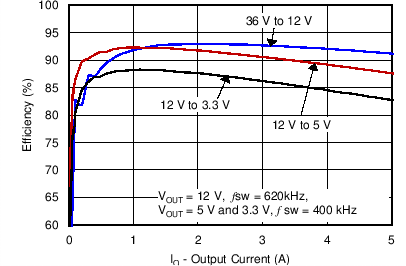

简化原理图 效率和负载电流间的关系

效率和负载电流间的关系