ZHCUAD3 January 2021 ADC3661 , ADC3662 , ADC3663

5 板载时钟硬件设置

板载 CDC 可用于一般评估,并免除用户对额外信号发生器的需求。然而,CDCE6214 的时钟杂散和抖动(由于 4.5 采样时钟/DCLKIN 关系而导致)开始影响更佳 ADC 交流性能。

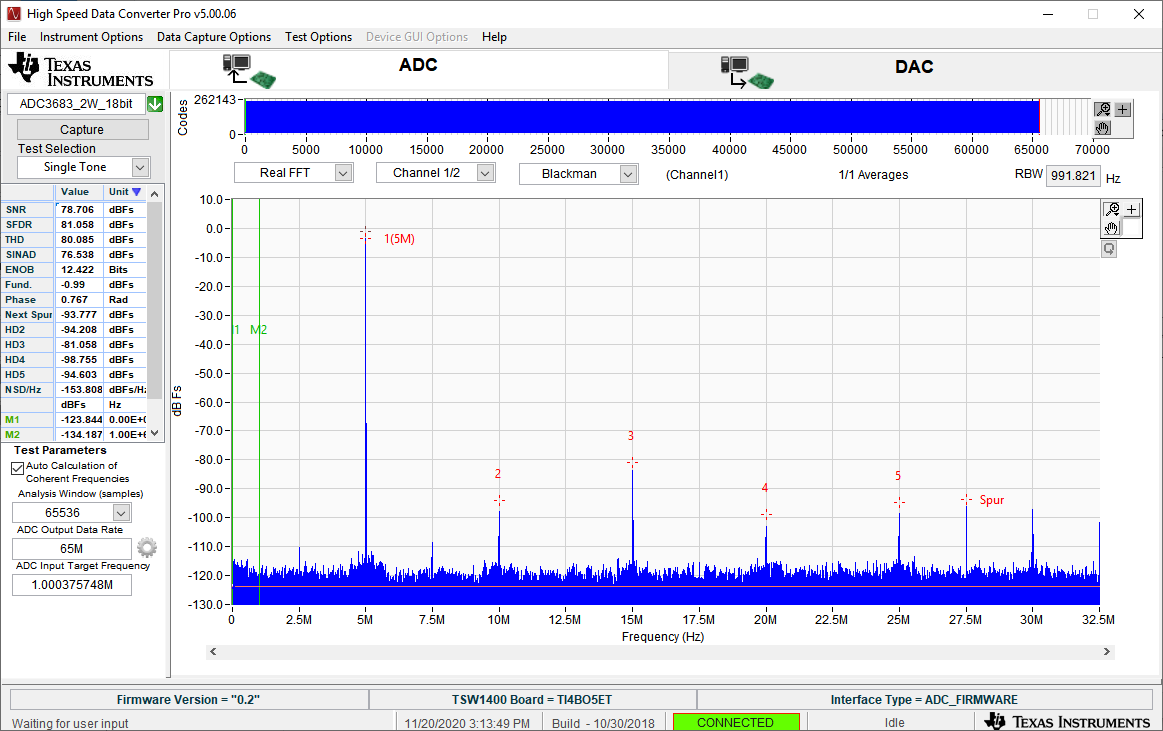

查看下图,我们可以看到 ADC3663EVM 的 SNR/SFDR 性能确实降低了几个 dBFS,但是,使用板载 CDCE6214 使用户无需提供外部采样时钟和 DCLKIN,并且可能有助于验证 FPGA 开发套件的 SLVDS 接口。在实践中,可以使用适当的滤波器来降低时钟杂散和宽带相位噪声的影响,以实现全面的 ADC 性能。

图 5-1 ADC3663EVM 板载时钟(CDCE6214:65MHz 采样时钟,260MHz DCLKIN)

图 5-1 ADC3663EVM 板载时钟(CDCE6214:65MHz 采样时钟,260MHz DCLKIN)下一节介绍如何配置 ADC366xEVM 并对其进行编程,以实现实时抽取模式的板载时钟操作。板载时钟也可用于旁路模式和复杂抽取模式,并使用本文档中概述的类似过程。

使用板载时钟时,在旁路和抽取模式下,有多种不同的采样率可供选择(65MSPS、25MSPS 和 10MSPS)。ADC35XX GUI 目前不支持将 CDCE6214 配置为这些预设选择之外的频率。