ZHCU939A May 2020 – October 2020

7.2.1 对 FPGA 进行编程

本节提供了对 FPGA 进行编程的说明。

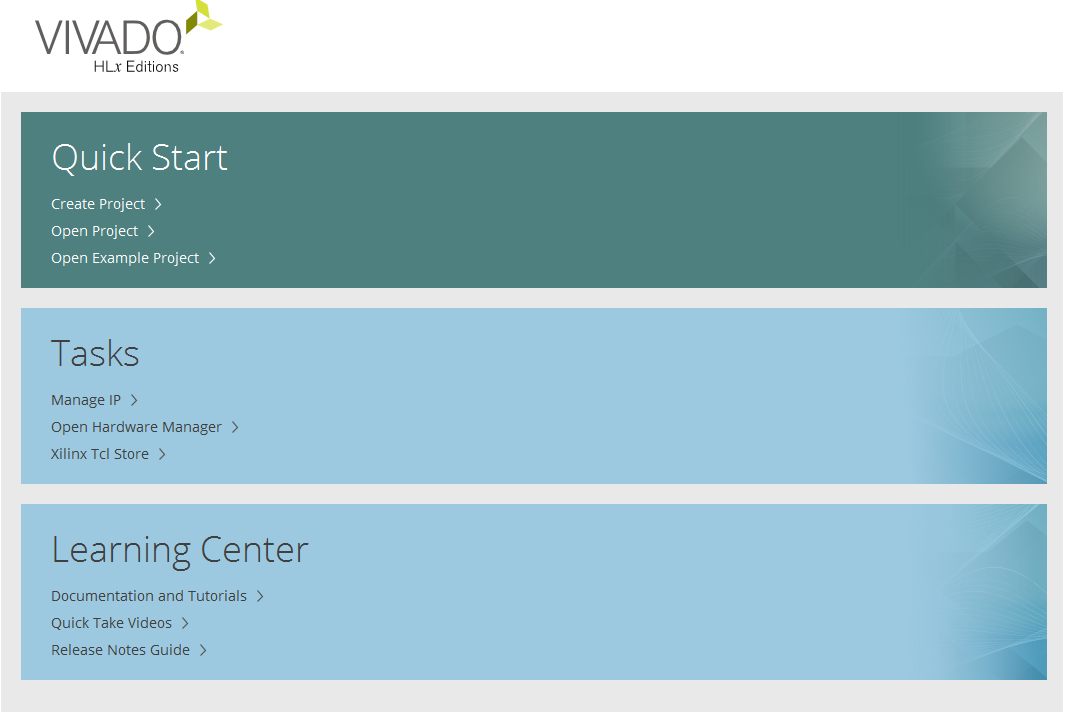

启动 Vivado 2019.1 并打开硬件管理器。

图 7-6 Vivado® 主菜单

图 7-6 Vivado® 主菜单选择“Open Target”(打开目标)。

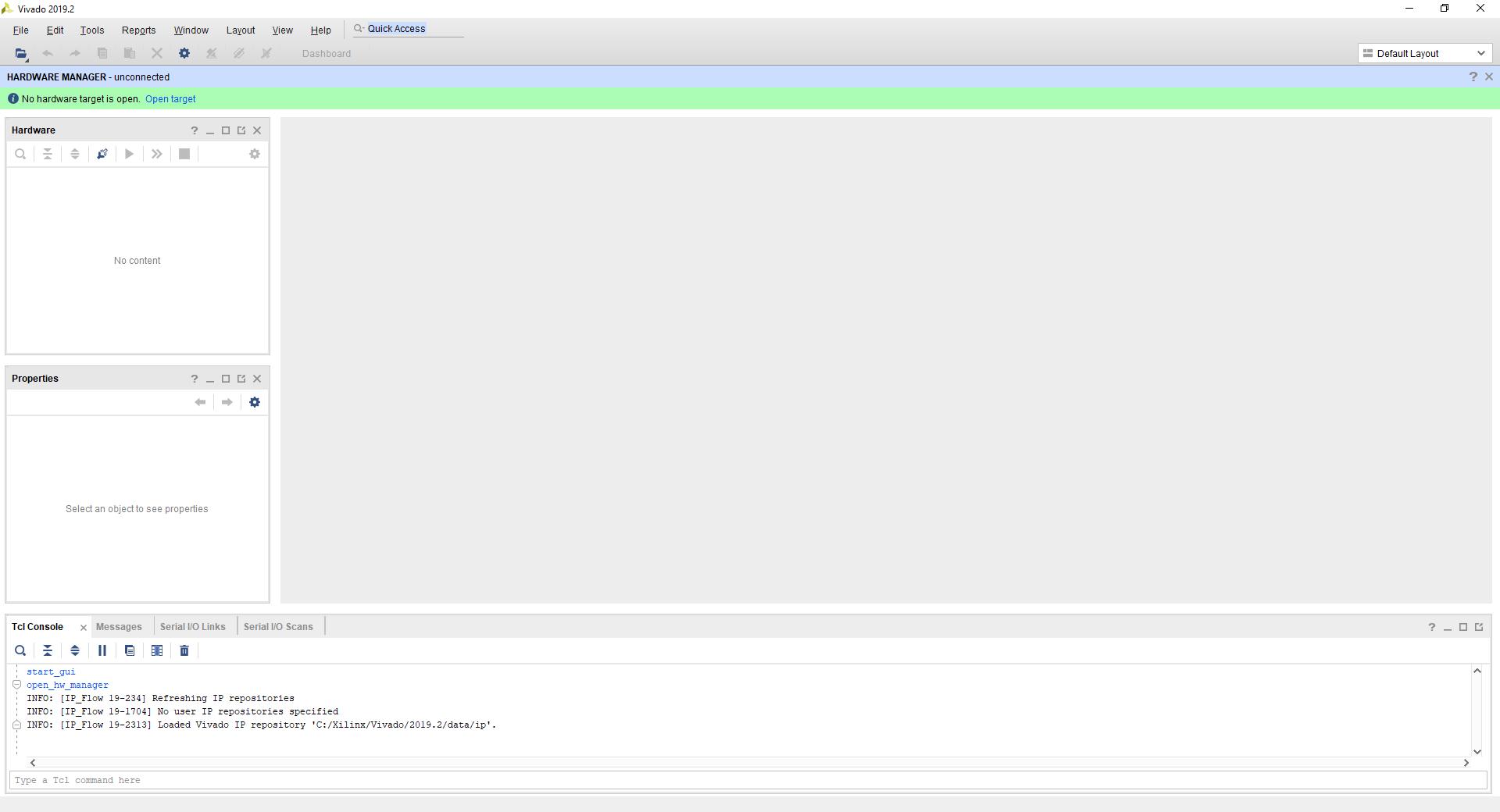

图 7-7 打开目标

图 7-7 打开目标选择“Auto Connect”(自动连接)

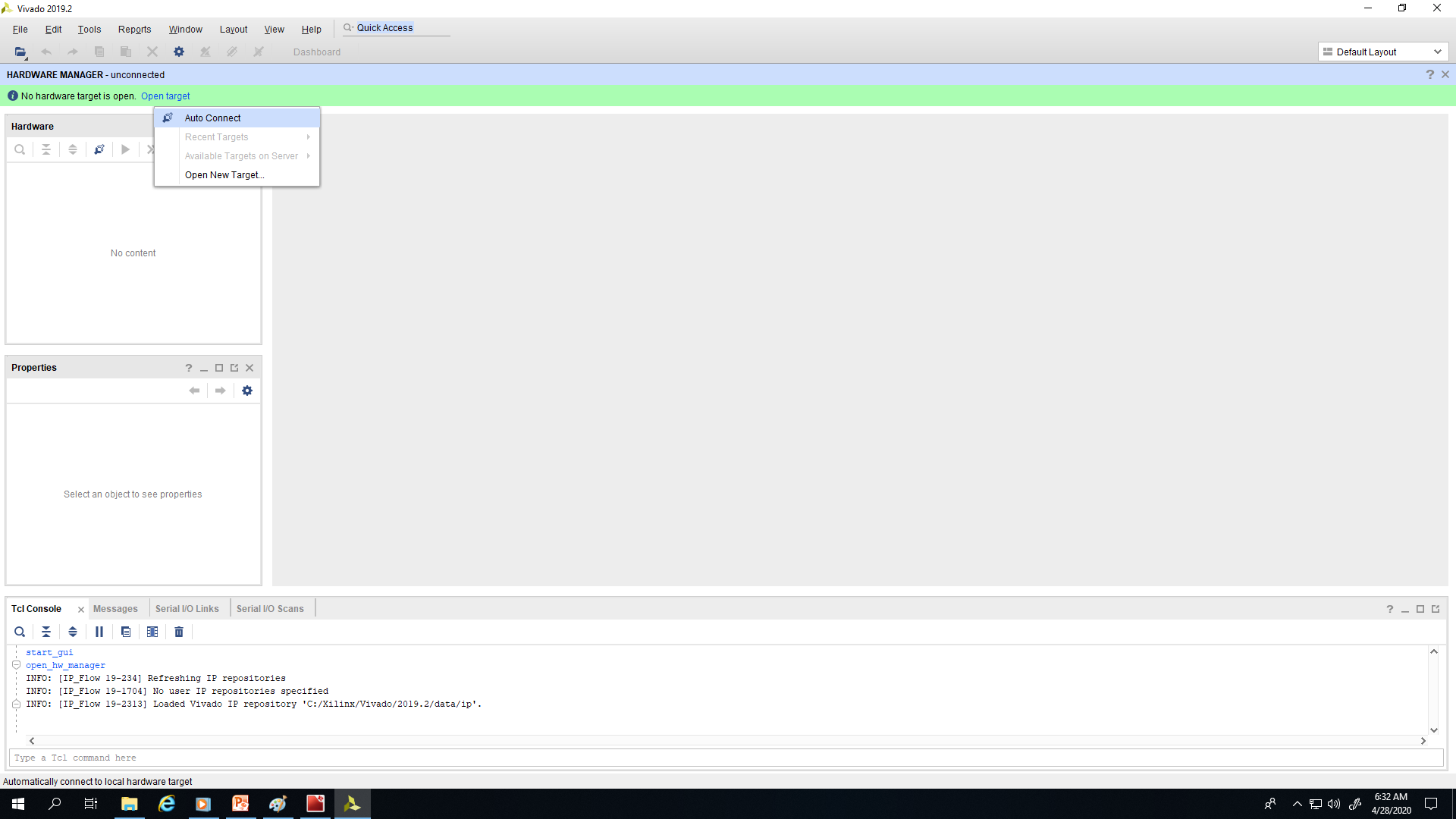

图 7-8 自动连接

图 7-8 自动连接右键点击 xcku060… 器件,然后选择“Program”(编程)。

图 7-9 选择器件

图 7-9 选择器件

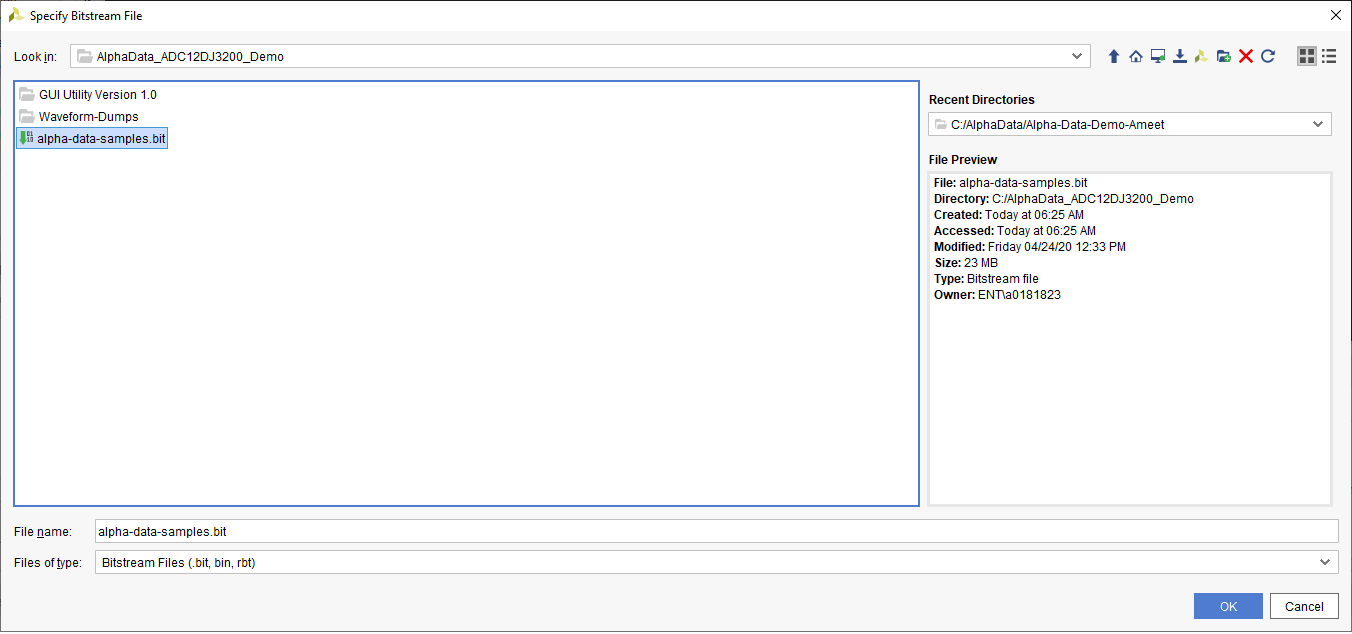

导航至 C:\AlphaData_ADC12DJ3200_Demo,然后选择文件“alpha-data-samples.bit”。

图 7-10 导航至位文件位置

图 7-10 导航至位文件位置点击 Program(编程)按钮以使用位文件完成 FPGA 配置。

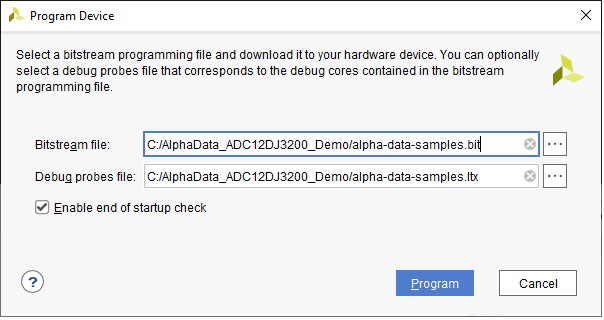

图 7-11 使用位文件对器件进行编程

图 7-11 使用位文件对器件进行编程在 Vivado TCL 控制台中,执行以下命令:

- cd c:/AlphaData_ADC12DJ3200_Demo

- source setup_new.txt

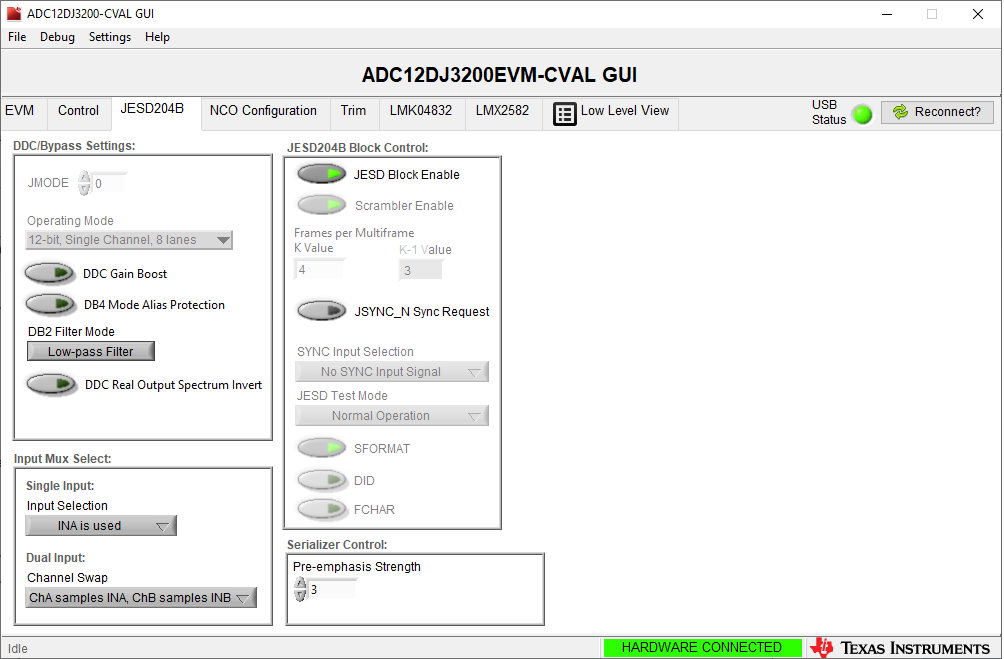

切换回 ADC12DJ3200EVM-CVAL GUI。

导航至“JESD204B”选项卡并点击“JSYNC_N Sync Request”(JSYNC_N Sync 请求)按钮(它现在应该处于关闭状态,如图 7-12 所示)。

切换回 Vivado 设置。

在 Vivado TCL 控制台中,执行以下命令:

cd c:/AlphaData_ADC12DJ3200_Demo

source capture_new.txt

FPGA 现在将连续捕获 ADC 数据。

图 7-12 将 ADC SYNC 设置为高电平

图 7-12 将 ADC SYNC 设置为高电平