ZHCU939A May 2020 – October 2020

7.2 对 ADC12DJ3200EVM SYNC 进行手动操作

本节详细介绍了对 ADC12DJ3200EVM SYNC 进行手动操作。

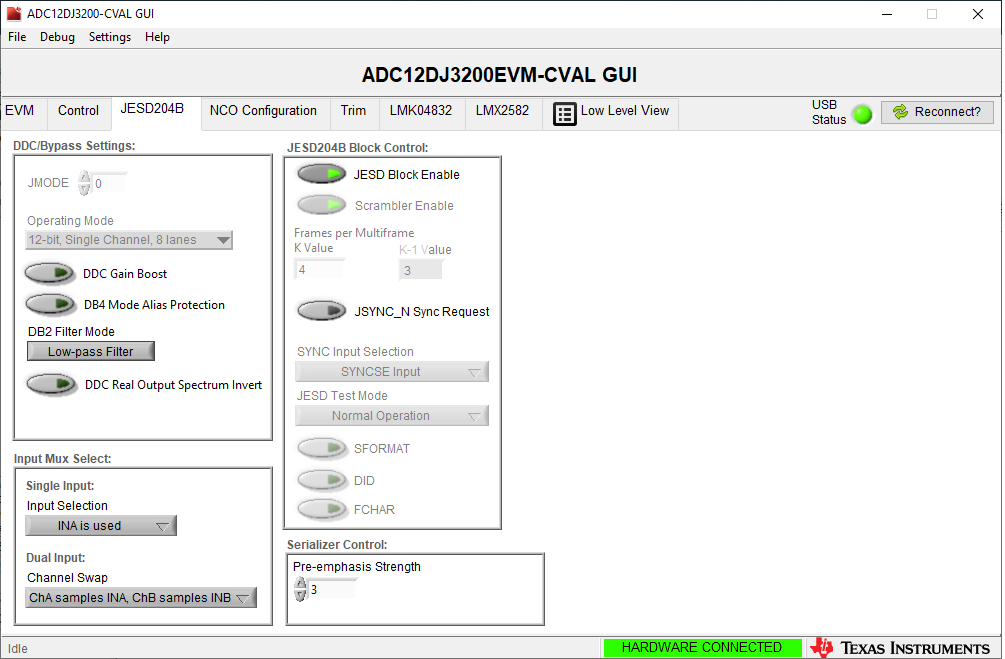

- 在 ADC12DJ3200EVM-CVAL GUI 中,点击“JESD204B”选项卡,如图 7-3 所示。

图 7-3 “JESD204B”选项卡

图 7-3 “JESD204B”选项卡 - 执行以下步骤(按顺序):

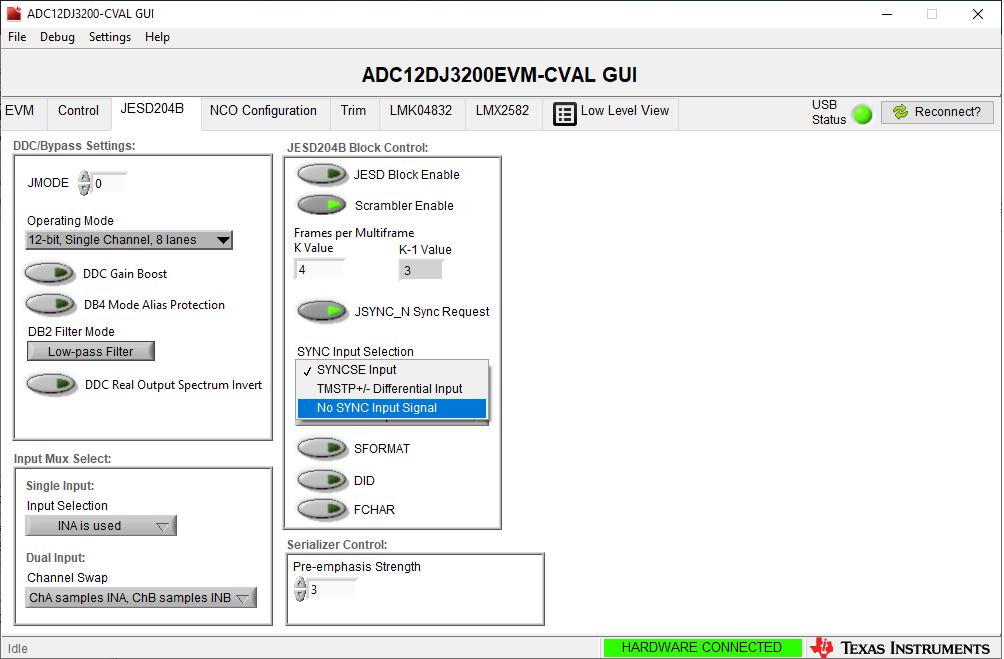

- 点击“JESD Block Enable”以将其禁用(绿色箭头不应亮起)。

- 点击“SFORMAT”按钮(启用它)。FPGA 固件使用无符号数据和 K 值 4。

- 点击“JSYNC_N Sync _Request”按钮(它应该启用或“亮起”)。

- 从“SYNC Input Selection”下拉菜单中选择“No SYNC Input Signal”。

图 7-4 使用软件设置 ADC SYNC

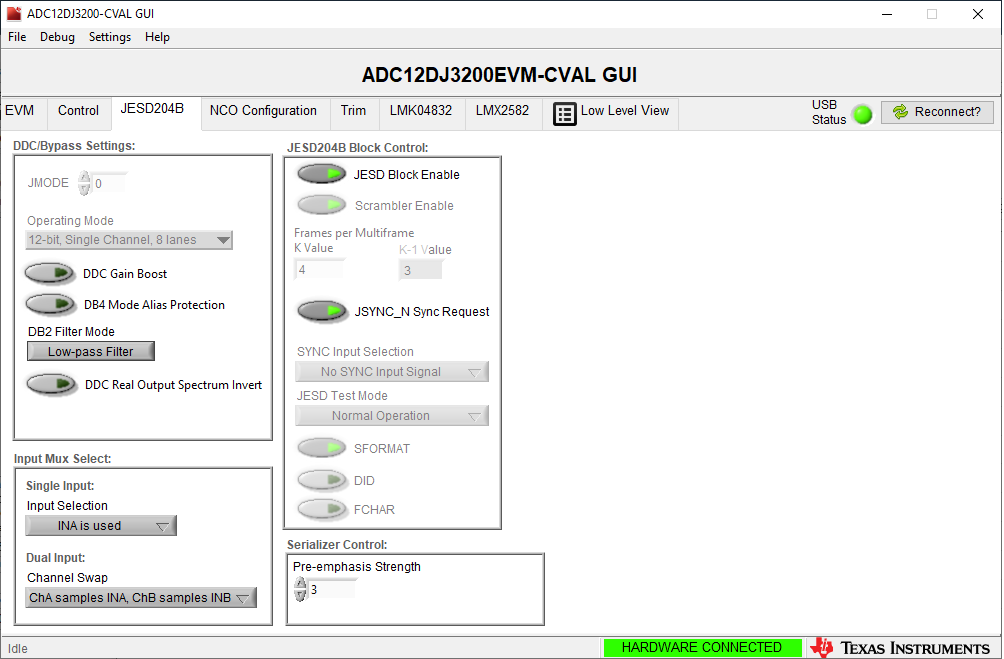

图 7-4 使用软件设置 ADC SYNC - 点击“JESD Block Enable”(启用它)。现在 GUI 应该如图 7-5 所示。

图 7-5 ADC 内部 SYNC 现已设为低电平

图 7-5 ADC 内部 SYNC 现已设为低电平