ZHCAFB4 April 2025 TPSI3100 , TPSI3100-Q1

2.1 电路启动行为

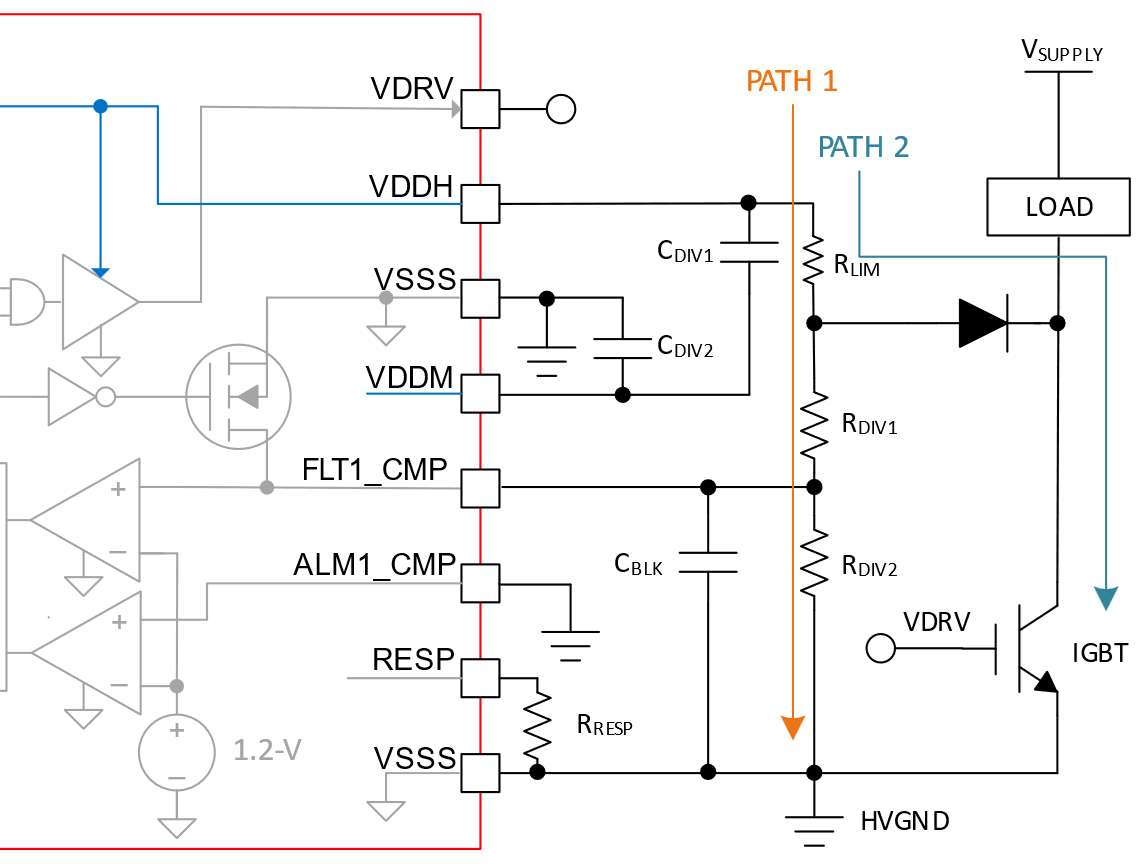

在 EN 为低电平上电时,TPSI3133 接收电力并开始将电力传输到其次级电源轨(VDDM 和 VDDH)。内部 MOSFET 将比较器输入拉低,以避免误触发。一旦 EN 变为高电平,两个电流路径(路径 1 和 2)将竞争以设置比较器输入电压,如 图 2-1 所示。由于 IGBT 导通延迟,路径 1 通常比路径 2 快,因此一旦 EN 变为高电平,TPSI3133 就会将比较器输入额外下拉保持 100ns,从而让 IGBT 在检测到故障之前完全导通。添加消隐电容 (CBLK) 可以提供额外的延迟,但必须仔细选择,以尽量减少应力时间。在过载情况下,IGBT 的 VCE 上升,导致 HV 二极管阳极上的电压升高,从而触发故障比较器阈值。一旦 TPSI3133 检测到故障,它就会关闭驱动器,进而关闭 IGBT,从而保护系统。

图 2-1 DESAT KVL 路径

图 2-1 DESAT KVL 路径