ZHCABY3B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

9.2 接地布局注意事项

系统地是电路板上与噪声和 EMI 问题相关的最关键区域和基础。要更大限度地减少这些问题,最实用的方法是使用单独的接地平面。

什么是接地噪声?

来自电路(例如驱动器)的每个信号都有一个通过接地路径流向其来源的返回电流。随着频率升高,甚至对于继电器等简单但高电流的开关,由于存在线路阻抗,因此会产生压降,进而会在接地方案中产生干扰。返回路径始终是阻力最小的路径。对于直流信号,这将是电阻最小的路径;对于高频信号,它将是阻抗最小的路径。这说明了接地平面如何简化该问题,并且是确保信号完整性的关键。

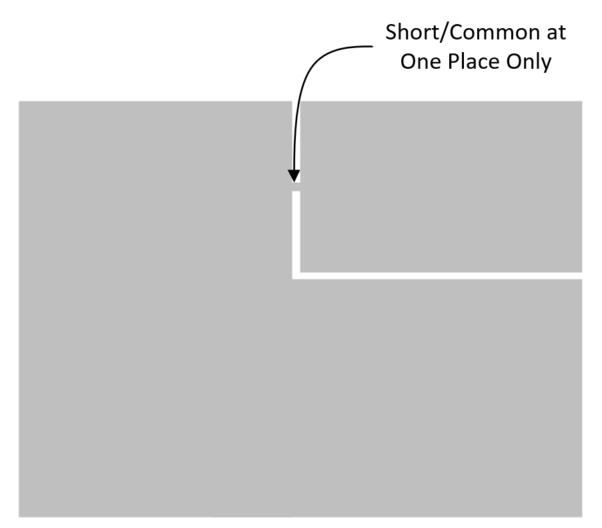

不建议数字返回信号在模拟返回(接地)区域内传播;因此,设计人员必须分离接地平面,以将所有数字信号返回环路保持在其接地区域内。在完成这种分离时应该要仔细。许多设计使用单个(通用)稳压器来生成具有相同电压电平(例如 3.3V)的数字和模拟电源。您需要将模拟电源轨和数字电源轨及其各自接地端相互隔离。隔离接地端时请小心,因为两个接地都必须在某处短接。图 9-2 展示了如何防止数字信号的可能返回路径形成一个通过模拟接地的环路。在每个设计中,考虑元件放置方式等因素来确定公共点。请勿添加与任何接地布线串联的任何电感器(铁氧体磁珠)或电阻器(甚至不是 0Ω)。由于高频下的相关电感,阻抗会增加,从而会导致电压差。请勿将以数字地为基准的信号路由到模拟地或其他方向。

图 9-2 数字地和模拟地以及公共区域

图 9-2 数字地和模拟地以及公共区域