SNLU254A November 2020 – July 2022

4.4 DS160PT801 Local Decoupling

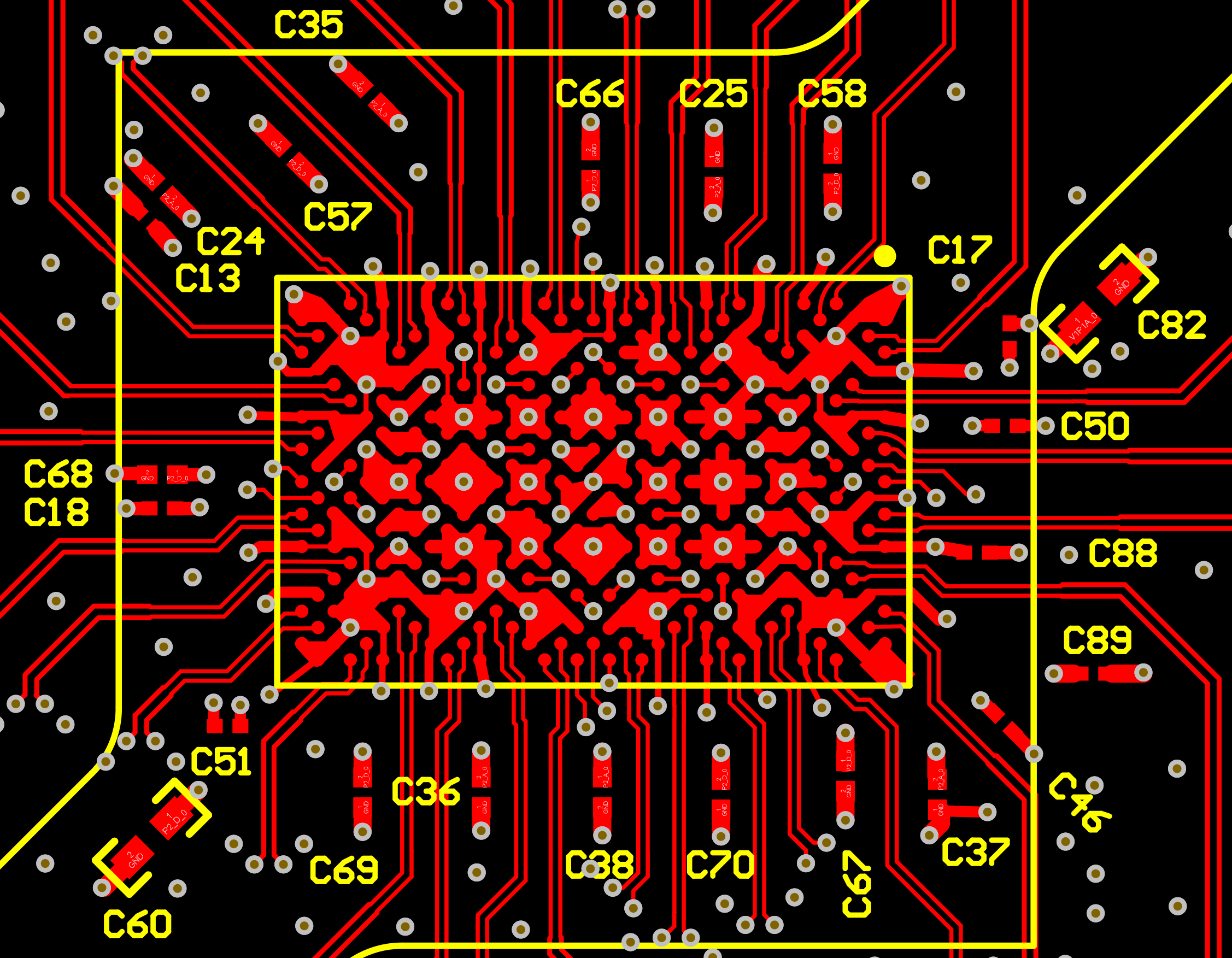

To complement the PCB power layers, decoupling capacitors have been arranged to filter device noise. The design of the high-current analog and digital decoupling uses Top and Bottom layer capacitors to optimize the overall frequency response of the decoupling solution.

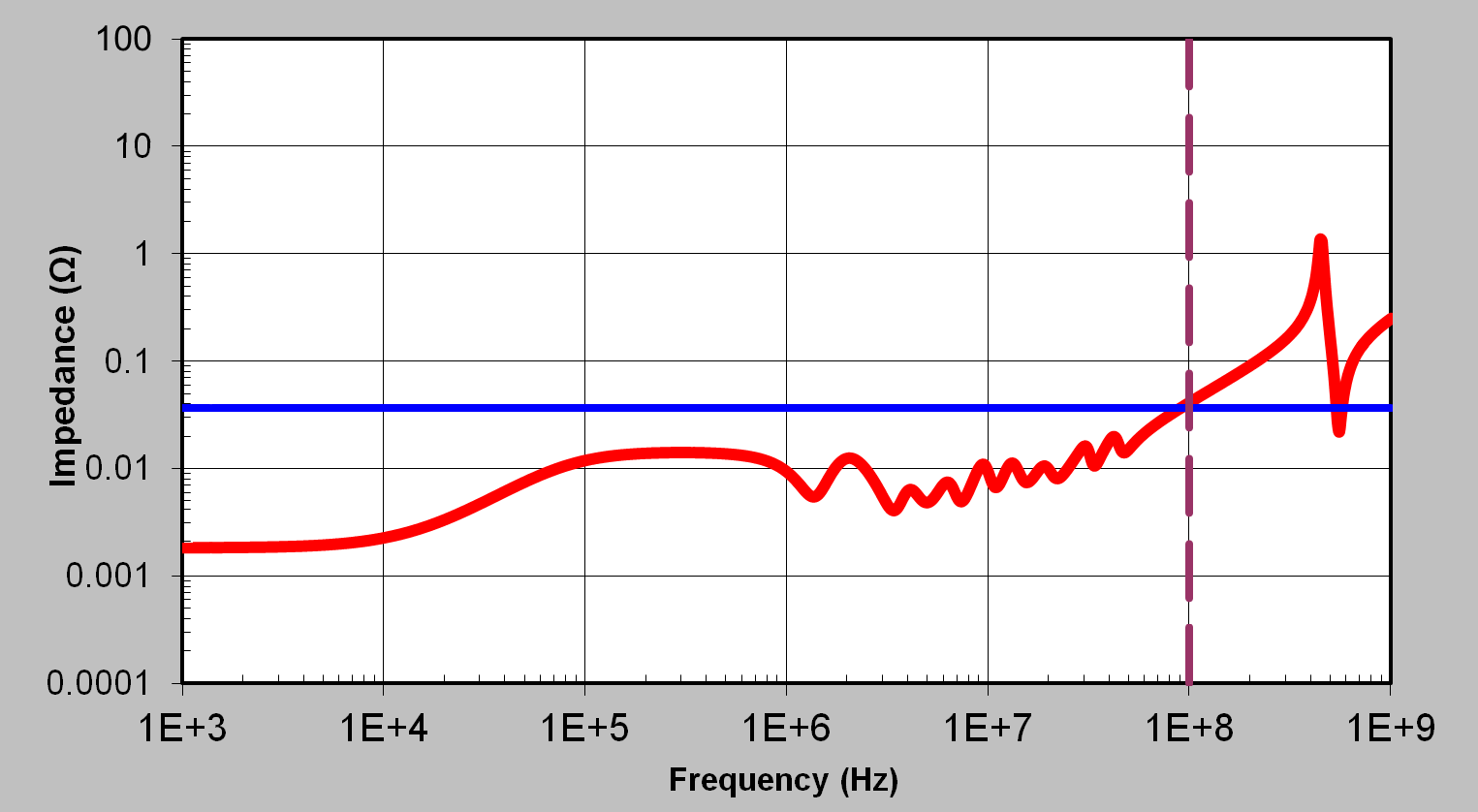

Figure 4-5 Decoupling Solution Frequency Response

Extending the targeted frequency range out to 100 MHz ensures digital noise associated with the PCIe reference clock is minimized. The highest frequency components require very low inductance to perform well. Placing the high current supplies close to the top layer surface ensures the lowest inductance possible to the supply plane and ultimately to the device itself.

Figure 4-6 PCB Top Layer