SLAA721E October 2016 – March 2020 MSP430FR5969 , MSP430FR5969-SP , MSP430FR5994 , MSP430FR6989

- Trademarks

- 1Introduction

- 2Implementation

- 3Customization of MSP430FRBoot

- 4Building MSPBoot

- 5Demo Using FRAM LaunchPad Development Kit as Host

- 6Porting the target side example projects to other MSP430FR devices

- 7References

- 8Revision History

2.4.1.2 SPI

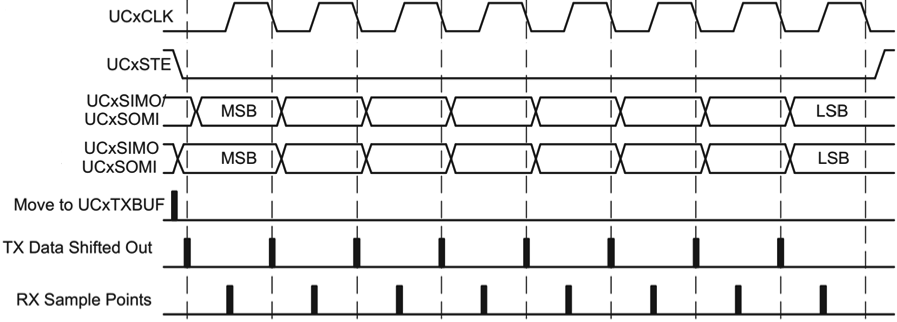

The SPI interface, used for CC110x communication, is implemented using the following configuration (also see Figure 2-7):

- 8-bit data

- MSB first

- Clock polarity = 0 (inactive state is low)

- Clock phase = 1 (data captured on first clock edge, changed on following edge)

- 3-pin configuration with STE implemented using GPIO

Figure 2-7 SPI Format

Figure 2-7 SPI Format