ZHCSUT0D October 2001 – February 2024 TFP410

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3 Feature Description

- 6.4 Device Functional Modes

- 6.5 Programming

- 6.6

Register Maps

- 6.6.1 VEN_ID Register (Sub-Address = 01−00 ) [reset = 0x014C]

- 6.6.2 DEV_ID Register (Sub-Address = 03–02) [reset = 0x0410]

- 6.6.3 REV_ID Register (Sub-Address = 04) [reset = 0x00]

- 6.6.4 Reserved Register (Sub-Address = 07–05) [reset = 0x641400]

- 6.6.5 CTL_1_MODE (Sub-Address = 08) [reset = 0xBE]

- 6.6.6 CTL_2_MODE Register (Sub-Address = 09) [reset = 0x00]

- 6.6.7 CTL_3_MODE Register (Sub-Address = 0A) [reset = 0x80]

- 6.6.8 CFG Register (Sub-Address = 0B)

- 6.6.9 RESERVED Register (Sub-Address = 0E–0C) [reset = 0x97D0A9]

- 6.6.10 DE_DLY Register (Sub-Address = 32) [reset = 0x00]

- 6.6.11 DE_CTL Register (Sub-Address = 33) [reset = 0x00]

- 6.6.12 DE_TOP Register (Sub-Address = 34) [reset = 0x00]

- 6.6.13 DE_CNT Register (Sub-Address = 37–36) [reset = 0x0000]

- 6.6.14 DE_LIN Register (Sub-Address = 39–38) [reset = 0x0000]

- 6.6.15 H_RES Register (Sub-Address = 3B−3A)

- 6.6.16 V_RES Register (Sub-Address = 3D−3C)

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- PAP|64

散热焊盘机械数据 (封装 | 引脚)

- PAP|64

订购信息

3 说明

TFP410 器件是德州仪器 (TI) 的 PanelBus™ 平板显示产品,是符合 DVI 1.0 标准的全系列端到端解决方案的一部分,面向 PC 和消费类电子产品行业。

TFP410 器件提供了一个通用接口,可以无缝连接到常用的图形控制器。该通用接口的一些优势包括可选总线宽度、可调信号电平以及差分和单端时钟。1.1V 至 1.8V 可调数字接口提供了一条与 12 位或 24 位接口无缝连接的低 EMI 高速总线。DVI 接口以 24 位真彩像素格式支持高达 165MHz 的 UXGA 平板显示器分辨率。

TFP410 器件将 PanelBus 电路创新与 TI 先进的 0.18μm EPIC-5 CMOS 工艺技术和 TI 的超低接地电感 PowerPAD 封装相结合,从而得到一个紧凑的 64 引脚 TQFP 封装,提供可靠、低电流、低噪声、高速数字接口解决方案。

(1) 有关更多信息,请参阅节 10

(2) 封装尺寸(长 × 宽)为标称值,并包括引脚(如适用)。

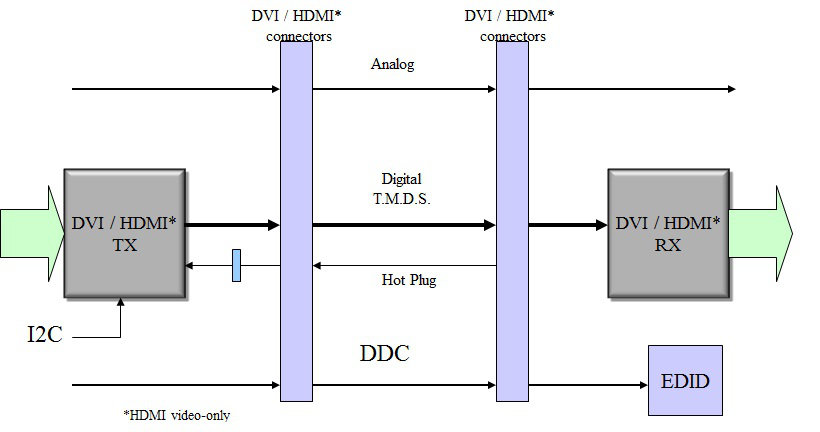

典型的 HDMI 接口

典型的 HDMI 接口