ZHCACF8 march 2023 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.9 执行最终瞬态分析

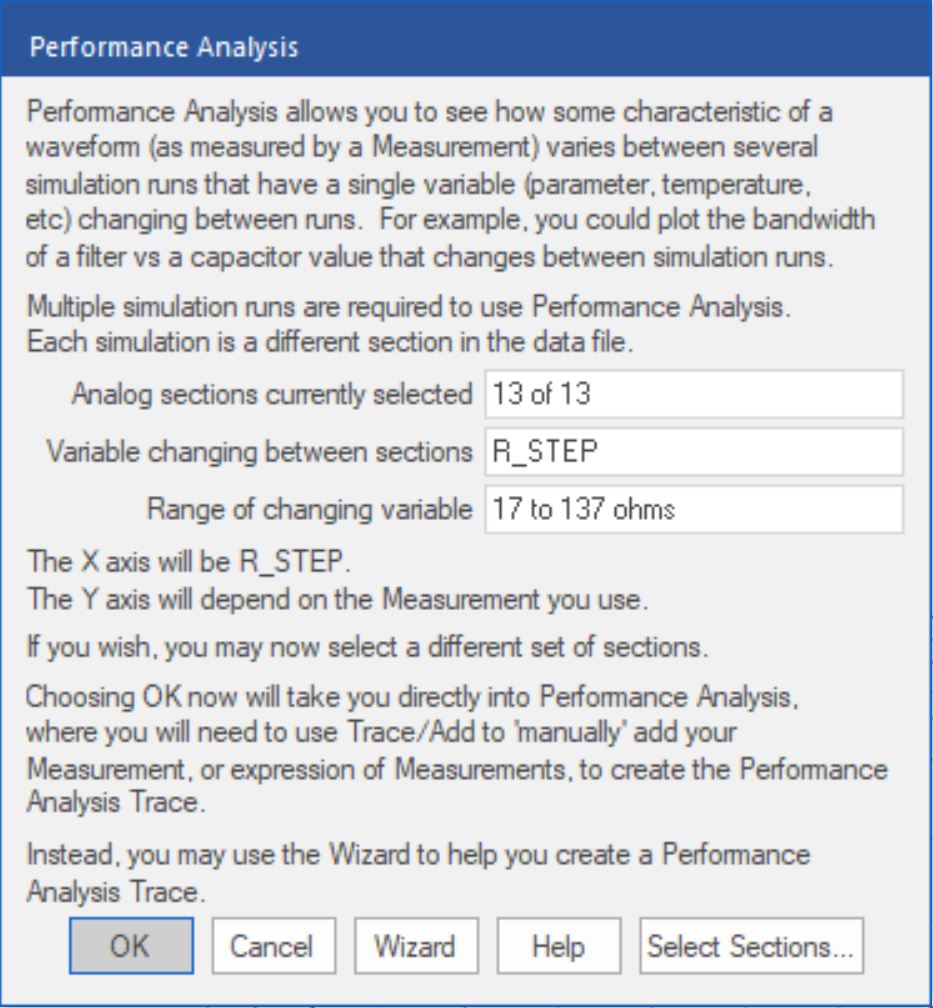

作为节 3.8中介绍的迭代方法的替代方法,性能分析工具可用于更好地选择 Rs 的理想值。通过将性能分析工具应用于图 3-12 中显示的初始扫描结果,可以将建立误差表示为 Rs 值的函数。要启动性能分析工具,请使用 PSpice for TI 仿真窗口左上角的菜单转到“Trace”➔“Performance Analysis...”。性能分析工具如图 3-15 所示。

图 3-15 F280049 性能分析示例

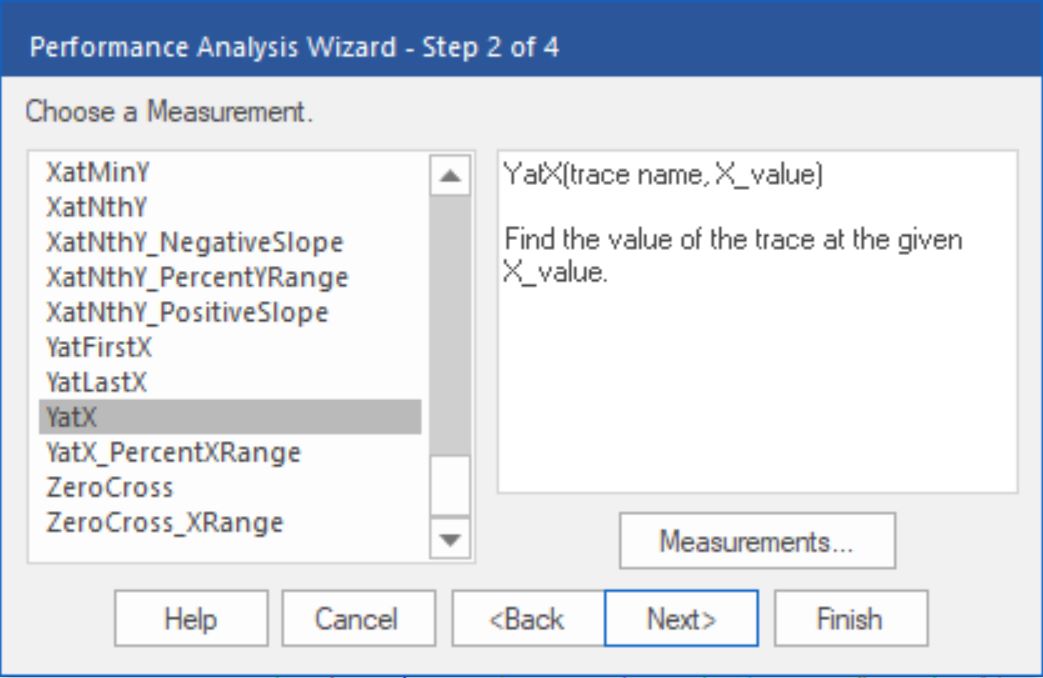

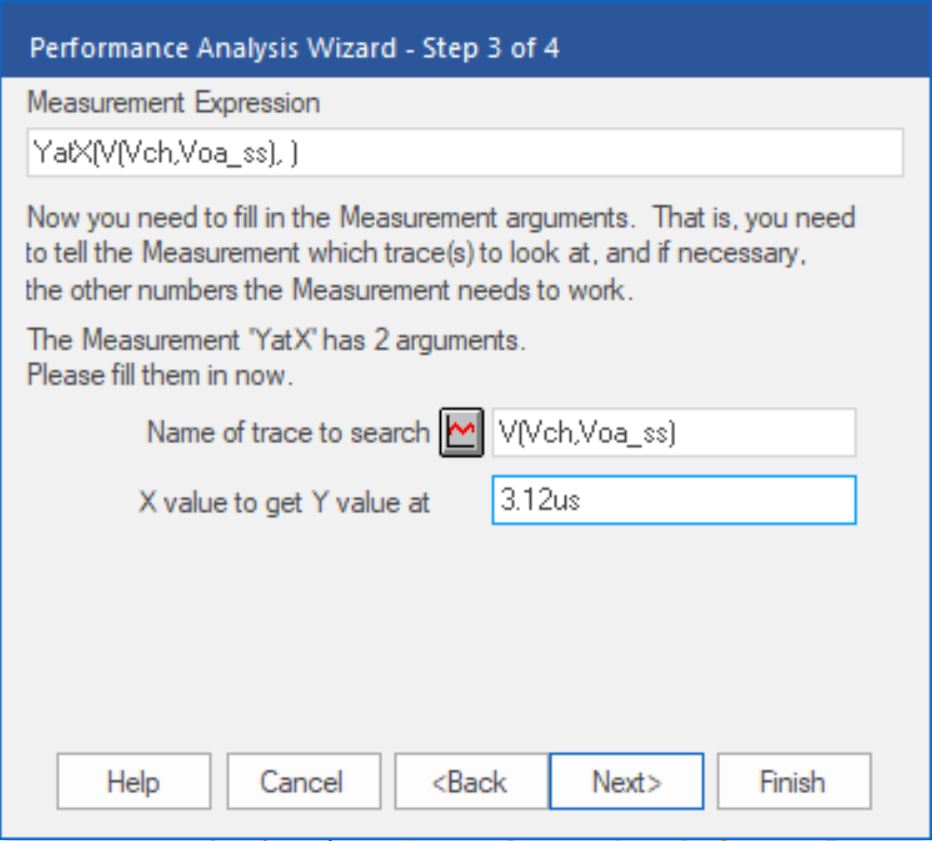

图 3-15 F280049 性能分析示例使用“Wizard”创建性能分析迹线。当系统提示您选择测量值时,请选择“YatX”,如图 3-16 所示。当系统提示您完成测量表达式时,请输入 V(Vch, Voa_ss) 作为要搜索的迹线的名称,输入 3.12µs 作为测量 Y 值的 X 值,如图 3-17 所示。请注意,该测量表达式测量 Verror 迹线在 3.12µs 处的 Y 值,3.12µs 恰好在采集窗口结束后。因此,该测量表达式测量建立误差。

图 3-16 F280049 性能分析向导示例 - 第 2 步,共 4 步

图 3-16 F280049 性能分析向导示例 - 第 2 步,共 4 步 图 3-17 F280049 性能分析向导示例 - 第 3 步,共 4 步

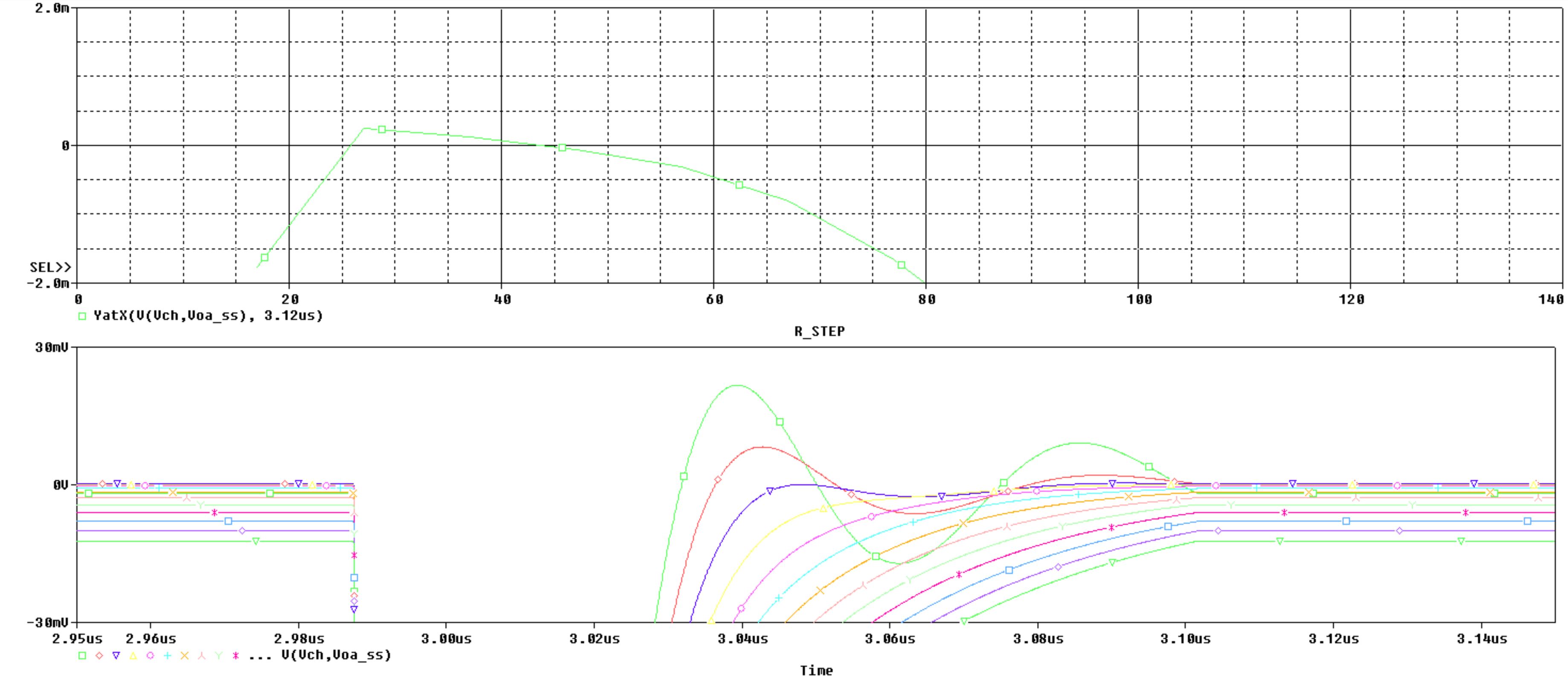

图 3-17 F280049 性能分析向导示例 - 第 3 步,共 4 步使用“Wizard”完成操作后,系统将显示作为 Rs 值函数的建立误差性能分析迹线,如图 3-18 所示。请注意,建立误差标度已调整为显示 -2mV 至 +2mV 的范围。通过双击垂直轴并修改“Data Range”,可以根据需要进一步调整建立误差标度。

图 3-18 F280049 性能分析迹线示例

图 3-18 F280049 性能分析迹线示例查看性能分析迹线可以发现,当 Rs 值约为 26Ω 时,建立误差约为零,而当 Rs 值约为 44Ω 时,建立误差再次约为零。但是,图 3-12 表明,相比较大 Rs 值,较小 Rs 值往往会导致较大的 Verror 振荡。较大的 Verror 振荡并不理想,因为采集窗口持续时间的微小变化会导致建立误差发生较大变化。此外,Rs 值接近 26Ω 时的性能分析迹线斜率比 Rs 值接近 44Ω 时的性能分析迹线斜率更陡。较陡的性能分析迹线斜率并不可取,因为 Rs 值的微小变化会导致建立误差的较大变化。因此,约为 26Ω 的 Rs 值被忽略,取而代之的是约为 44Ω 的 Rs 值。

根据性能分析迹线,介于 24Ω 和 56Ω(含)之间的任何 Rs 值都将实现充分建立。因此,可以从 24Ω 至 56Ω(含)范围内的一组标准电阻值中选择 Rs 的最终值,优先选择接近 44Ω 的标准电阻值。Rs 的理想值是该范围内可提供最小建立误差的标准电阻值。根据性能分析迹线,该范围内提供最小建立误差的 5% 标准电阻值为 43Ω。因此,选择 Rs 的最终值作为理想值,即 43Ω。