ZHCAEY9 January 2025 LMX1205

3 该请求模式是什么?

请求模式有助于获得无干扰的系统参考输出 (SYS0-SYS3)。SYS0-SYS3 支持不同的输出模式,如 表 3-1 所示。

| SYSREF_MODE (R19<1:0>) | 系统参考运行模式 |

|---|---|

| 0 | 连续模式 |

| 1 | 脉冲模式 |

| 2 | 中继器非同步模式 |

| 3 | 中继器同步模式 |

对于本应用手册波形,使用了 LMX1205 多点电路板,其中存在 3 个器件,即 primary,两个 secondary(secondary1 和 secondary2)。下面的 图 3-1 显示了多点电路板的顶层布置。

图 3-1 多个 LMX1205 配置

图 3-1 多个 LMX1205 配置表 3-2 总结了用于在多点电路板上获取波形的配置。secondary1 和 secondary2 器件具有相同的配置。引脚的命名依据 LMX1205 低噪声、高频 JESD 缓冲器/倍频器/分频器,数据表。

| 主器件 | 引脚名称(引脚编号) | 格式 | Secondary1 器件 | 引脚名称(引脚编号) | 格式 |

|---|---|---|---|---|---|

| 输入 | CLKIN_P (6)/ CLKIN_N (7) | 交流耦合 | 输入 | CLKIN_P (6)/ CLKIN_N (7) | 交流耦合 |

| SYSREFREQ_P (2)/ SYSREFREQ_N (3) | 50Ohm 端接 | SYSREFREQ_P (2)/ SYSREFREQ_N (3) | 直流耦合 | ||

| 输出 | CLKOUT2_P (33)/ CLKOUT2_N (32) | 交流耦合 | 输出 | CLKOUT2_P (33)/ CLKOUT2_N (32) | 交流耦合 |

| SYSREFOUT2_P (30)/ SYSREFOUT2_N (29) | 交流耦合 | SYSREFOUT2_P (33)/ SYSREFOUT2_N (32) | 交流耦合 |

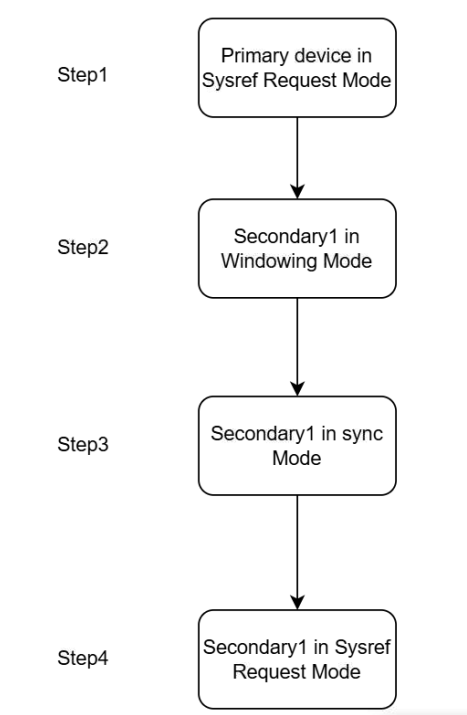

图 3-2 中所示的流程图,其中突出显示了当 secondary1 器件(由主器件的 CH0 输出驱动)应为确定性时要执行的步骤序列。与 Secondary2 器件的情况相同,但主器件输出的不同通道 (CH1) 驱动输入引脚。

图 3-2 LMX1205 多点电路板上的事件序列

图 3-2 LMX1205 多点电路板上的事件序列假设需要设置 secondary1 和 secondary2 器件,使其始终是确定性的。在 图 3-2 中的步骤 1,中加载 tics pro 详细信息(请参阅附录步骤 1),使主器件处于系统参考请求模式。主 SYSREFOUT0/1_P/N 的输出驱动 secondary 1 和 2 的 SYSREFREQ_P/N 输入引脚,需要将相应的输入设置写入该特定器件。表 3-3 总结了不同的端接配置。

| SYSREFREQ_VCM(R16<1:0>) | 引脚 2、3 (SYSREFREQ_P/N) 的输入模式 |

|---|---|

| 0 | 交流耦合 |

| 1 | 引脚 P 偏置为高于引脚 M(交流耦合) |

| 2 | 引脚 M 偏置为高于引脚 P(交流耦合) |

| 3 | 直流耦合 |

多点电路板拥有所讨论的 3 个器件。存在板载多路复用器,根据选择线路,一次仅写入一个器件。SEL0 和 SEL1 是两个选择行,可通过 user controls -> Pins 选项卡下的 tics-pro GUI 进行配置。在写入任何设备之前,请确保通过 表 3-4 选择了设备。

| SEL1 | SEL0 | 需写入的器件 |

|---|---|---|

| 0 | 0 |

初级 |

| 0 | 1 | Secondary1 |

| 1 | 0 | Secondary2 |

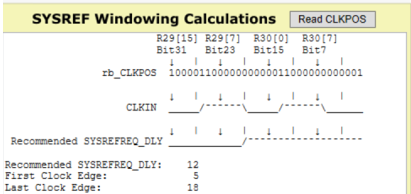

在主器件上加载 tics pro 文件后,主器件输出上可以连续显示系统参考信号。如果需要在主输出端启用脉冲模式,请使用 SPI 寄存器 SYSREFREQ_INPUT (R17<7:6>) 在主输入引脚 2 处提供从低电平到高电平的脉冲、方法是从 1(十进制)切换到 3 (十进制)并将 SYSREF_MODE 切换为 1。这可以在脉冲模式下在初级侧的系统参考输出端生成脉冲。Secondary1 和 Secondary2 需要使用 tics-pro 保持在窗口模式(请参阅附录步骤 2)并在主输出端生成脉冲。在执行窗口化之前,为寄存器 SYSREFREQ_CLR (R17<2>) 提供 1 到 0 的切换。从 secondary1 器件和 secondary2 器件读取窗口化代码 (rb_CLKPOS R30<15:0>)。如果初级输出端有连续信号,在每次从低电平到高电平转换时,窗口化会在 secondary1 和 secondary2 中持续发生。窗口化回读不断变化,因此避免需要将 SYSWND_UPDATE_STOP (R17<5>) 设置为 1。在 secondary1 和 secondary2 器件中写入 SYSREFREQ_DLY 位置寄存器。这可以确保 secondary1 和 secondary2 引脚的上升沿始终可以通过一些内部延迟在时钟输入的下降沿对齐。

在 "Calculations" 选项卡下,可以检查要写入 SYSREFREQ_DLY 寄存器的值。按下 "Read CLKPOS" 检查按钮后,该器件会自动读取 rb_CLKPOS 并计算 SYSREFREQ_DLY 值。对于这种情况,如下图所示,要写入的 SYSREFREQ_DLY 为 12。这是 10GHz 输入时钟的一个示例。如 图 3-3 所示为 1GHz 的类似窗口化快照作为时钟输入。

图 3-3 系统参考窗口化 Tics-pro 快照详细信息 10GHz

图 3-3 系统参考窗口化 Tics-pro 快照详细信息 10GHz 图 3-4 系统参考窗口化 Tics-pro 快照详细信息 1GHz

图 3-4 系统参考窗口化 Tics-pro 快照详细信息 1GHz将 secondary1 和 secondary2 器件设置为同步模式,如 表 2-1 所示。在 primary 输出端到 secondary 1 和 secondary 2 输出端(引脚 3 和引脚 4)生成脉冲,这可以确保 secondary1 和 secondary2 都同步,并且可以是确定性的。

要写入 secondary1 和 secondary2 以使器件在窗口化后同步的寄存器:

- SYSREFREQ_DLY

- SYSREFREQ_CLR ->1-->0 切换

- SYSREFREQ_MODE -->0

- SYNC_STOP-->1

在先前的寄存器写入之后,secondary1 和 secondary2 都会同步。将 secondary1 和 secondary2 设备设置为系统参考请求模式,如 表 3-1 所示。图 3-5 显示了主模式处于连续模式,secondary 1 和 secondary2 处于连续模式的配置。

SYSREFREQ_MODE -->1 进入请求模式。如 图 3-5 所示,seconadary1 和 secondary2 器件都是确定性的。

图 3-5 连续模式下 Primary、Secondary1 和 Secondary2 的同步波形

图 3-5 连续模式下 Primary、Secondary1 和 Secondary2 的同步波形黄色:Continuous Primary sysrefout2_p

红色:连续性 Secondary1 sysrefout2_p

绿色:连续性 Secondary2 sysrefout2_p

用于上一个示例的频率:

CLKIN 为 1GHz,主 sysrefout2_p 为 3.125MHz、Secondary1/2 sysrefout2_p 为 31.25MHz

如果更改 CLKIN 的频率,请确保 IQ 分频器值 SYSREF_DLY_DIV(R20<15:14>) 和频率范围设置 (SYSREF_DLY_SCALE R16<7:6>),如数据表中所示。

如前面所示,作为初级侧处于连续模式,当引脚 3 为低电平时,不会出现任何系统参考。这可以通过使用 SPI 将 secondary1 和 secondary2 上的引脚 3 从内部拉高来避免,如 表 3-5 所示。

| SYSREFREQ_INPUT(R17<7:6>) | 引脚 2、3 (SYSREFREQ_P/N) 的输入模式 |

|---|---|

| 0 | SYSREFREQ 引脚值 |

| 1 | 通过 SPI 在内部下拉至低电平 |

| 2 | 不适用 |

| 3 | 通过 SPI 在内部拉至高电平 |

图 3-6 Primary、Secondary1 和 Secondary2 与连续模式下的连续 Secondary1 和 Secondary2 的同步波形

图 3-6 Primary、Secondary1 和 Secondary2 与连续模式下的连续 Secondary1 和 Secondary2 的同步波形如 图 3-6 所示,Secondary1 和 Secondary2 器件输入均绕过初级连续脉冲。

如 表 3-1 所,述关于不同的系统参考输出模式,请参阅以下部分以了解输出波形的外观。