ZHCACD6A February 2023 – December 2023 AM62A3 , AM62A3-Q1 , AM62A7 , AM62A7-Q1 , AM62P , AM62P-Q1

3.6.4 仿真结果

为 LPDDR4 接口提供了 10 层设计的仿真结果。必须满足这些仿真目标,以确保设计将在所需的性能水平上运行。

需要在 DRAM 引脚/BGA 上验证 CA 仿真。其中包括:

- Vix_CK 比率 (JEDEC)

- 与眼图模板相关的抖动/噪声容限 (JEDEC)

- 峰-峰值电源噪声

图 3-10 CA 的 LPDDR4 仿真结果

图 3-10 CA 的 LPDDR4 仿真结果需要在 DRAM BGA 引脚和 DRAM 焊盘上验证数据写入仿真。其中包括:

- Vix_CK 比率 (JEDEC)

- 与眼图模板相关的抖动/噪声容限 (JEDEC)

- 峰-峰值电源噪声

图 3-11 写入的 LPDDR4 仿真结果

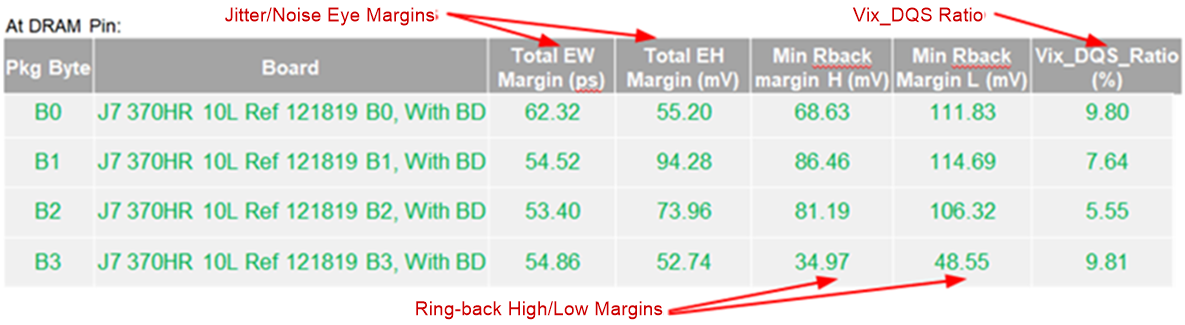

图 3-11 写入的 LPDDR4 仿真结果需要在 SOC 上验证数据读取仿真。其中包括:

- 与眼图模板相关的抖动/噪声容限

- 峰-峰值电源噪声

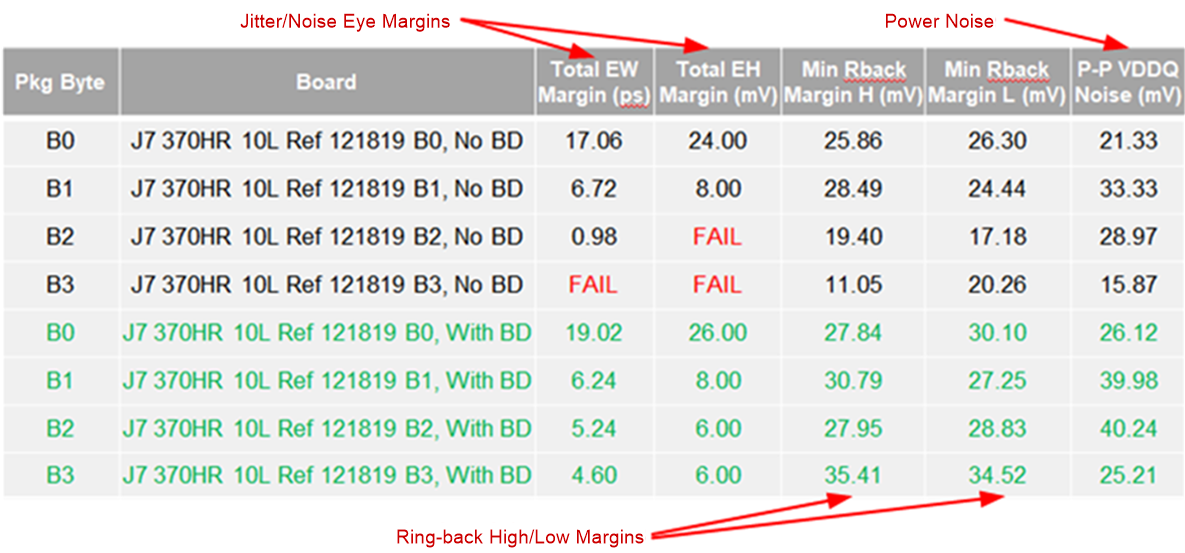

图 3-12 读取的 LPDDR4 仿真结果

图 3-12 读取的 LPDDR4 仿真结果读取的仿真结果包含两组数据,即黑色数据和绿色数据。黑色数据表示设计失败,因为几个字节未能满足眼图裕量。绿色数据是同一设计的仿真结果,但对过孔残桩应用了背钻。