ZHCAB57C January 2020 – January 2024 TLV320ADC3120 , TLV320ADC3140 , TLV320ADC5120 , TLV320ADC5140 , TLV320ADC6120 , TLV320ADC6140

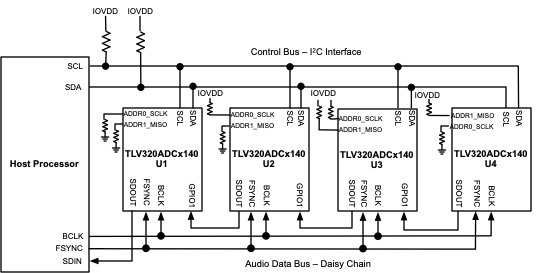

3.2 菊花链 TDM 的 ASI 配置

为了简化电路板布线和 TDM 总线时序要求,或避免高 SDOUT 线路负载电容,TLV320ADCx140/PCMx140-Q1 器件提供菊花链模式,将一个器件的数据输出 (SDOUT) 作为输入路由到另一器件的 GPI1 引脚 (GPIO1)。每个器件在内部将数据合并到 TDM 总线的相应时隙中,并将其传递给下一个器件。

图 3-12 TLV320ADCx140/PCMx140-Q1 菊花链 TDM 连接图

图 3-12 TLV320ADCx140/PCMx140-Q1 菊花链 TDM 连接图按表 3-8 所示设置 ASI_CFG2 寄存器的 ASI_DAISY 位字段可将器件配置为菊花链配置。

图 3-13 ASI_CFG2 寄存器

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ASI_DAISY | 保留 | ASI_ERR | ASI_ERR_ RCOV |

保留 | |||

| R/W-0h | R-0h | R/W-0h | R/W-0h | R-0h | |||

表 3-8 ASI_CFG2 寄存器字段说明

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 7 | ASI_DAISY | R/W | 0h | ASI 菊花链连接 0d = 所有器件都连接在通用 ASI 总线中 1d = 所有器件都以菊花链形式连接 ASI 总线 |

| 6 | 保留 | R | 0h | 保留 |

| 5 | ASI_ERR | R/W | 0h | ASI 总线错误检测 0d = 启用总线错误检测 1d = 禁用总线错误检测 |

| 4 | ASI_ERR_RCOV | R/W | 0h | ASI 总线错误自动恢复 0d = 启用总线错误恢复后自动恢复 1d = 禁用总线错误恢复后自动恢复,并在主机配置器件之前保持断电状态 |

| 3-0 | 保留 | R | 0h | 保留 |

对于将 SDOUT 作为输入路由到另一器件的 GPIO1 引脚的所有器件,必须将 GPIO_CFG0 寄存器的 GPIO1_CFG 位设置为菊花链的 ASI 输入 (SDIN),如表 3-9 所示。

图 3-14 GPIO_CFG0 寄存器

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| GPIO1_CFG[3:0] | 保留 | GPIO1_DRV[2:0] | |||||

| R/W-2h | R-0h | R/W-2h | |||||

表 3-9 GPIO_CFG0 寄存器字段说明

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 7-4 | GPIO1_CFG[3:0] | R/W | 2h | GPIO1 配置 0d = GPIO1 禁用 1d = GPIO1 配置为通用输出 (GPO) 2d = GPIO1 配置为器件中断输出 (IRQ) 3d = GPIO1 配置为辅助 ASI 输出 (SDOUT2) 4d = GPIO1 配置为 PDM 时钟输出 (PDMCLK) 5d 至 7d = 保留 8d = GPIO1 配置为控制 MICBIAS 何时开启或关闭的输入 (MICBIAS_EN) 9d = GPIO1 配置为通用输入 (GPI) 10d = GPIO1 配置为控制器时钟输入 (MCLK) 11d = GPIO1 配置为菊花链的 ASI 输入 (SDIN) 12d = GPIO1 配置为通道 1 和通道 2 的 PDM 数据输入 (PDMDIN1) 13d = GPIO1 配置为通道 3 和通道 4 的 PDM 数据输入 (PDMDIN2) 14d = GPIO1 配置为通道 5 和通道 6 的 PDM 数据输入 (PDMDIN3) 15d = GPIO1 配置为通道 7 和通道 8 的 PDM 数据输入 (PDMDIN4) |

| 3 | 保留 | R | 0h | 保留 |

| 2-0 | GPIO1_DRV[2:0] | R/W | 2h | GPIO1 输出驱动配置(当 GPIO1 配置为 SDOUT2 时不使用) 0d = 高阻态输出 1d =驱动低电平有效和高电平有效 2d = 驱动低电平有效和弱高电平 3d = 驱动低电平有效和高阻态 4d = 驱动低电平有效和高电平有效 5d = 驱动高阻态和高电平有效 6d 至 7d =保留 |

以图 3-12 为例,以下 I2C 脚本将 U1、U2 和 U3 配置为菊花链,通过链的 GPIO1 从 SDOUT 中的下一个器件接收输入。注意,每个器件的通道都映射到时隙 0-3。然而,在 U1 的 SDOUT 中,0-3 时隙用于 U1 通道,4-7 时隙用于 U2 通道,8-11 时隙用于 U3 通道,12-15 时隙用于 U4 通道。注意,菊花链中的最后一个器件不需要配置为菊花链模式,因为它不从其他器件获取 GPIO1 上的输入。

w 98 0B 00 # Set U1 Ch1 mapped to slot 0 of SDOUT

w 98 0C 01 # Set U1 Ch2 mapped to slot 1 of SDOUT

w 98 0D 02 # Set U1 Ch3 mapped to slot 2 of SDOUT

w 98 0E 03 # Set U1 Ch4 mapped to slot 3 of SDOUT

w 9A 0B 00 # Set U2 Ch1 mapped to slot 0 of SDOUT

w 9A 0C 01 # Set U2 Ch2 mapped to slot 1 of SDOUT

w 9A 0D 02 # Set U2 Ch3 mapped to slot 2 of SDOUT

w 9A 0E 03 # Set U2 Ch4 mapped to slot 3 of SDOUT

w 9C 0B 00 # Set U3 Ch1 mapped to slot 0 of SDOUT

w 9C 0C 01 # Set U3 Ch2 mapped to slot 1 of SDOUT

w 9C 0D 02 # Set U3 Ch3 mapped to slot 2 of SDOUT

w 9C 0E 03 # Set U3 Ch4 mapped to slot 3 of SDOUT

w 9E 0B 00 # Set U4 Ch1 mapped to slot 0 of SDOUT

w 9E 0C 01 # Set U4 Ch1 mapped to slot 1 of SDOUT

w 9E 0D 02 # Set U4 Ch1 mapped to slot 2 of SDOUT

w 9E 0E 03 # Set U4 Ch1 mapped to slot 3 of SDOUT

w 98 09 80 # Set U1's ASI to daisy chain

w 98 21 B0 # Set U1's GPIO1 input as ASI input for daisy chain

w 9A 09 80 # Set U2's ASI to daisy chain

w 9A 21 B0 # Set U2's GPIO1 input as ASI input for daisy chain

w 9C 09 80 # Set U3's ASI to daisy chain

w 9C 21 B0 # Set U3's GPIO1 input as ASI input for daisy chain