ZHCAB57C January 2020 – January 2024 TLV320ADC3120 , TLV320ADC3140 , TLV320ADC5120 , TLV320ADC5140 , TLV320ADC6120 , TLV320ADC6140

3.1 共享 TDM 的 ASI 配置

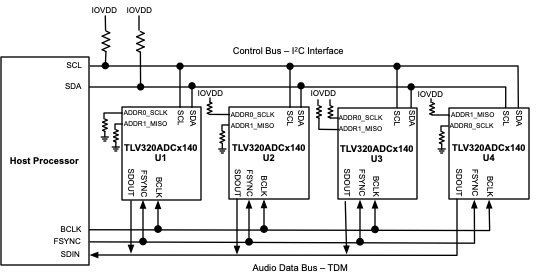

在共享 TDM 总线配置中,多个 TLV320ADCx140/PCMx140-Q1 器件的 ASI 总线连接在一起,形成一个共享总线,如图 3-2 所示。

图 3-2 TLV320ADCx140/PCMx140-Q1 共享 TDM 连接图

图 3-2 TLV320ADCx140/PCMx140-Q1 共享 TDM 连接图为了避免多个器件在同一时隙中传输输出数据,TLV320ADCx140/PCMx140-Q1 支持使用以下寄存器将器件的输入通道映射到可编程时隙:

- ASI_CH1(页 0x00,寄存器 0x0B),如图 3-3 所示

- ASI_CH2(页 0x00,寄存器 0x0C),如图 3-4 所示

- ASI_CH3(页 0x00,寄存器 0x0D),如图 3-5 所示

- ASI_CH4(页 0x00,寄存器 0x0E),如图 3-6 所示

这样就可以将任何通道以任何顺序映射到任何时隙。此外,TLV320ADCx140/PCMx140-Q1 还支持辅助 SDOUT 输出 (SDOUT2),这通过 GPO_CFG0 寄存器(位字段 GPIO1_CFG 值为 0x03)进行配置,如图 3-14 所示。这样一个或多个器件便可通过两个引脚输出时隙:主要输出 (SDOUT) 和辅助输出 (SDOUT2)。ASI_CHx 寄存器位字段 CHx_OUTPUT 将时隙映射到主要输出 (SDOUT) 或辅助输出 (SDOUT2)。

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 保留 | CH1_OUTPUT | CH1_SLOT[5:0] | |||||

| R-0h | R/W-0h | R/W-0h | |||||

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 7 | 保留 | R | 0h | 保留 |

| 6 | CH1_OUTPUT | R/W | 0h | 通道 1 输出线路 0d = 通道 1 输出在 ASI 主要输出引脚 (SDOUT) 上 1d = 通道 1 输出在 ASI 辅助输出引脚(GPIO1 或 GPOx)上 |

| 5-0 | CH1_SLOT[5:0] | R/W | 0h | 通道 1 时隙分配 0d = TDM 是时隙 0 或 I2S,LJ 是左侧时隙 0 1d = TDM 是时隙 1 或 I2S,LJ 是左侧时隙 1 2d 至 30d = 分配的时隙视配置而定 31d = TDM 是时隙 31 或 I2S,LJ 是左侧时隙 31 32d = TDM 是时隙 32 或 I2S,LJ 是右侧时隙 0 33d = TDM 是时隙 33 或 I2S,LJ 是右侧时隙 1 34d 至 62d = 分配的时隙视配置而定 63d = TDM 是时隙 63 或 I2S,LJ 是右侧时隙 31 |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 保留 | CH2_OUTPUT | CH2_SLOT[5:0] | |||||

| R-0h | R/W-0h | R/W-1h | |||||

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 7 | 保留 | R | 0h | 保留 |

| 6 | CH2_OUTPUT | R/W | 0h | 通道 2 输出线路 0d = 通道 2 输出在 ASI 主要输出引脚 (SDOUT) 上 1d = 通道 2 输出在 ASI 辅助输出引脚(GPIO1 或 GPOx)上 |

| 5-0 | CH2_SLOT[5:0] | R/W | 1h | 通道 2 时隙分配 0d = TDM 是时隙 0 或 I2S,LJ 是左侧时隙 0 1d = TDM 是时隙 1 或 I2S,LJ 是左侧时隙 1 2d 至 30d = 分配的时隙视配置而定 31d = TDM 是时隙 31 或 I2S,LJ 是左侧时隙 31 32d = TDM 是时隙 32 或 I2S,LJ 是右侧时隙 0 33d = TDM 是时隙 33 或 I2S,LJ 是右侧时隙 1 34d 至 62d = 分配的时隙视配置而定 63d = TDM 是时隙 63 或 I2S,LJ 是右侧时隙 31 |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 保留 | CH3_OUTPUT | CH3_SLOT[5:0] | |||||

| R-0h | R/W-0h | R/W-2h | |||||

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 7 | 保留 | R | 0h | 保留 |

| 6 | CH3_OUTPUT | R/W | 0h | 通道 3 输出线路 0d = 通道 3 输出在 ASI 主要输出引脚 (SDOUT) 上 1d = 通道 3 输出在 ASI 辅助输出引脚(GPIO1 或 GPOx)上 |

| 5-0 | CH3_SLOT[5:0] | R/W | 2h | 通道 3 时隙分配 0d = TDM 是时隙 0 或 I2S,LJ 是左侧时隙 0 1d = TDM 是时隙 1 或 I2S,LJ 是左侧时隙 1 2d 至 30d = 分配的时隙视配置而定 31d = TDM 是时隙 31 或 I2S,LJ 是左侧时隙 31 32d = TDM 是时隙 32 或 I2S,LJ 是右侧时隙 0 33d = TDM 是时隙 33 或 I2S,LJ 是右侧时隙 1 34d 至 62d = 分配的时隙视配置而定 63d = TDM 是时隙 63 或 I2S,LJ 是右侧时隙 31 |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 保留 | CH4_OUTPUT | CH4_SLOT[5:0] | |||||

| R-0h | R/W-0h | R/W-3h | |||||

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 7 | 保留 | R | 0h | 保留 |

| 6 | CH4_OUTPUT | R/W | 0h | 通道 4 输出线路 0d = 通道 4 输出在 ASI 主要输出引脚 (SDOUT) 上 1d = 通道 4 输出在 ASI 辅助输出引脚(GPIO1 或 GPOx)上 |

| 5-0 | CH4_SLOT[5:0] | R/W | 3h | 通道 4 时隙分配 0d = TDM 是时隙 0 或 I2S,LJ 是左侧时隙 0 1d = TDM 是时隙 1 或 I2S,LJ 是左侧时隙 1 2d 至 30d = 分配的时隙视配置而定 31d = TDM 是时隙 31 或 I2S,LJ 是左侧时隙 31 32d = TDM 是时隙 32 或 I2S,LJ 是右侧时隙 0 33d = TDM 是时隙 33 或 I2S,LJ 是右侧时隙 1 34d 至 62d = 分配的时隙视配置而定 63d = TDM 是时隙 63 或 I2S,LJ 是右侧时隙 31 |

以图 3-2 为例,以下 I2C 脚本将 U1-U4 的输入通道分别配置到 TLV320ADCx140/PCMx140-Q1 的 0-15 时隙中。注意,时隙并未按顺序分配给每个器件的输入通道,以显示为 TDM 时隙分配通道的灵活性:

w 98 0B 04 # Set U1 Ch1 mapped to slot 4 of SDOUT

w 98 0C 06 # Set U1 Ch2 mapped to slot 6 of SDOUT

w 98 0D 01 # Set U1 Ch3 mapped to slot 1 of SDOUT

w 98 0E 00 # Set U1 Ch4 mapped to slot 0 of SDOUT

w 9A 0B 03 # Set U2 Ch1 mapped to slot 3 of SDOUT

w 9A 0C 05 # Set U2 Ch2 mapped to slot 5 of SDOUT

w 9A 0D 02 # Set U2 Ch3 mapped to slot 2 of SDOUT

w 9A 0E 07 # Set U2 Ch4 mapped to slot 7 of SDOUT

w 9C 0B 08 # Set U3 Ch1 mapped to slot 8 of SDOUT

w 9C 0C 09 # Set U3 Ch2 mapped to slot 9 of SDOUT

w 9C 0D 0A # Set U3 Ch3 mapped to slot 10 of SDOUT

w 9C 0E 0C # Set U3 Ch4 mapped to slot 12 of SDOUT

w 9E 0B 0F # Set U4 Ch1 mapped to slot 15 of SDOUT

w 9E 0C 0D # Set U4 Ch1 mapped to slot 13 of SDOUT

w 9E 0D 0E # Set U4 Ch1 mapped to slot 14 of SDOUT

w 9E 0E 0B # Set U4 Ch1 mapped to slot 11 of SDOUT这种配置要求所有器件将其输出置于高阻抗模式,以便另一器件可以驱动总线。TLV320ADCx140/PCMx140-Q1 支持通过 ASI_CFG0 寄存器位字段 TX_FILL,在未使用的位时钟周期内将输出线路驱动为低电平或置于高阻抗状态,如图 3-7 所示。设置 TX_FILL 会将主要输出线路 (SDOUT) 和辅助输出线路 (SDOUT2) 置于高阻抗。注意,复位值会将 SDOUT 和 SDOUT2 配置为在未使用的位时钟周期期间驱动为低电平。

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ASI_FORMAT[1:0] | ASI_WLEN[1:0] | FSYNC_POL | BCLK_POL | TX_EDGE | TX_FILL | ||

| R/W-0h | R/W-3h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | ||

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 7-6 | ASI_FORMAT[1:0] | R/W | 0h | ASI 协议格式 0d = TDM 模式 1d = I2S 模式 2d = LJ(左对齐)模式 3d = 保留 |

| 5-4 | ASI_WLEN[1:0] | R/W | 3h | ASI 字长或时隙长度 0d = 16 位 1d = 20 位 2d = 24 位 3d = 32 位 |

| 3 | FSYNC_POL | R/W | 0h | ASI FSYNC 极性 0d = 极性默认符合标准协议 1d = 与标准协议的极性相反 |

| 2 | BCLK_POL | R/W | 0h | ASI BCLK 极性 0d = 极性默认符合标准协议 1d = 与标准协议的极性相反 |

| 1 | TX_EDGE | R/W | 0h | ASI 数据输出(在主要和辅助数据引脚上)发送边沿 0d = 边沿默认符合位 2 (BCLK_POL) 中的协议配置设置 1d = 与默认边沿设置的下一个边沿反相(半个周期延迟) |

| 0 | TX_FILL | R/W | 0h | 任何未使用周期的 ASI 数据输出(在主要和辅助数据引脚上) 0d = 针对未使用周期始终发送 0 1d = 针对未使用周期始终使用高阻态 |

TLV320ADCx140/PCMx140-Q1 还支持通过 ASI_OUT_CH_EN 寄存器对未使用的通道时隙进行三态设置,如图 3-8 所示。

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ASI_OUT_CH1_EN | ASI_OUT_CH2_EN | ASI_OUT_CH3_EN | ASI_OUT_CH4_EN | ASI_OUT_CH5_EN | ASI_OUT_CH6_EN | ASI_OUT_CH7_EN | ASI_OUT_CH8_EN |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 7 | ASI_OUT_CH1_EN | R/W | 0h | ASI 输出通道 1 使能设置 0d = 通道 1 输出时隙处于三态条件 1d = 通道 1 输出时隙已启用 |

| 6 | ASI_OUT_CH2_EN | R/W | 0h | ASI 输出通道 2 使能设置 0d = 通道 2 输出时隙处于三态条件 1d = 通道 2 输出时隙已启用 |

| 5 | ASI_OUT_CH3_EN | R/W | 0h | ASI 输出通道 3 使能设置 0d = 通道 3 输出时隙处于三态条件 1d = 通道 3 输出时隙已启用 |

| 4 | ASI_OUT_CH4_EN | R/W | 0h | ASI 输出通道 4 使能设置 0d = 通道 4 输出时隙处于三态条件 1d = 通道 4 输出时隙已启用 |

| 3 | ASI_OUT_CH5_EN | R/W | 0h | ASI 输出通道 5 使能设置 0d = 通道 5 输出时隙处于三态条件 1d = 通道 5 输出时隙已启用 |

| 2 | ASI_OUT_CH6_EN | R/W | 0h | ASI 输出通道 6 使能设置 0d = 通道 6 输出时隙处于三态条件 1d = 通道 6 输出时隙已启用 |

| 1 | ASI_OUT_CH7_EN | R/W | 0h | ASI 输出通道 7 使能设置 0d = 通道 7 输出时隙处于三态条件 1d = 通道 7 输出时隙已启用 |

| 0 | ASI_OUT_CH8_EN | R/W | 0h | ASI 输出通道 8 使能设置 0d = 通道 8 输出时隙处于三态条件 1d = 通道 8 输出时隙已启用 |

为了通过防止引脚悬空来更大限度地降低功耗,TLV320ADCx140/PCMx140-Q1 还支持在 SDOUT 和 SDOUT2 输出上启用总线保持器。寄存器 ASI_CFG1 通过 TX_KEEPER 位字段控制输出线路上的总线保持器,如表 3-7 所示。该寄存器还控制 SDOUT 和 SDOUT2 强烈驱动总线上的最低有效位 (LSB) 的时间长度。这样可以进行精细控制,确保两个器件不会同时在同一总线上驱动不同的信号,从而避免总线争用。例如,可以将 U2 的 LSB 设置为在位时钟周期的前半部分进行传输,而 U3 的 MSB 则在没有任何偏移的情况下进行驱动。此外,选择 TX_KEEPER 值 0x2 或 0x3 可确保主机处理器正确锁存 LSB 来增加系统的鲁棒性,因为总线保持器继续使用最后驱动的值来保持总线。注意,该寄存器还控制最高有效位 (MSB) 延迟的位时钟数。

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TX_LSB | TX_KEEPER[1:0] | TX_OFFSET[4:0] | |||||

| R/W-0h | R/W-0h | R/W-0h | |||||

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 7 | TX_LSB | R/W | 0h | 用于 LSB 传输的 ASI 数据输出(在主要和辅助数据引脚上) 0d = 一个完整周期内发送 LSB 1d = 在前半个周期内发送 LSB,在后半个周期内发送高阻态 |

| 6-5 | TX_KEEPER[1:0] | R/W | 0h | ASI 数据输出(在主要和辅助数据引脚上)总线保持器 0d = 始终禁用总线保持器 1d = 始终启用总线保持器 2d = 总线保持器仅在 LSB 传输期间启用一个周期 3d = 总线保持器仅在 LSB 传输期间启用 1.5 个周期 |

| 4-0 | TX_OFFSET[4:0] | R/W | 0h | ASI 数据 MSB 时隙 0 偏移(在主要和辅助数据引脚上) 0d = ASI 数据 MSB 位置没有偏移,并符合标准协议 1d = 一个 BCLK 周期相对于标准协议的 ASI 数据 MSB 位置(TDM 模式是时隙 0 或 I2S,LJ 模式是左侧和右侧时隙 0)偏移 2d = 两个 BCLK 周期相对于标准协议的 ASI 数据 MSB 位置(TDM 模式是时隙 0 或 I2S,、LJ 模式是左侧和右侧时隙 0)的偏移 3d 至 30d = 根据配置分配的 ASI 数据 MSB 位置(TDM 模式是时隙 0 或 I2S,LJ 模式是左侧和右侧时隙 0)偏移 31d = 31 个 BCLK 周期相对于标准协议的 ASI 数据 MSB 位置(TDM 模式是时隙 0 或 I2S,LJ 模式是左侧和右侧时隙 0)偏移 |

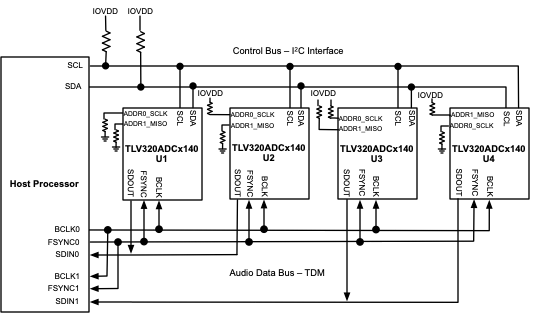

为了支持比方程式 1 所允许的更多时隙数,可通过多条主机处理器 TDM 总线将连接的 TLV320ADCx140/PCMx140-Q1 器件拆分开来,如图 3-10 所示。这种连接方法不仅使位时钟 (BCLK) 速度减半,而且还减少了主机处理器数据线路 SDIN1 和 SDIN2 上的负载电容。

图 3-10 TLV320ADCx140/PCMx140-Q1 共享拆分 TDM 连接图

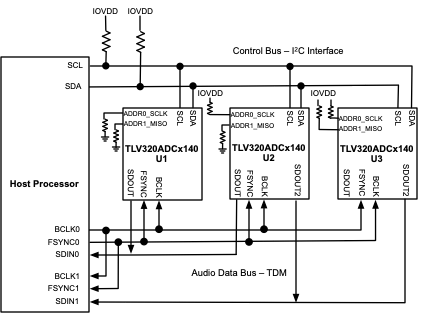

图 3-10 TLV320ADCx140/PCMx140-Q1 共享拆分 TDM 连接图另一种选择是使用辅助输出将单个器件的时隙映射到主要输出和辅助输出。例如,一个具有 12 个通道、32 位数据字且以 96KHz 采样速率运行的系统,需要 36.864MHz 的位时钟(三个器件 * 四个通道/器件 * 32 位字 * 96kHz),违反了 25MHz 的最大 BCLK 速度。12 个通道可以分开,其中 6 个通道分配给主要总线,另外 6 个通道分配给辅助总线,使 BCLK 保持在 25MHz 以下。每个器件有四个通道,一个器件有两个通道分配给主要总线,两个通道分配给辅助总线,如图 3-11 所示。

图 3-11 TLV320ADCx140/PCMx140-Q1 具有主要和辅助总线的共享拆分 TDM 连接图

图 3-11 TLV320ADCx140/PCMx140-Q1 具有主要和辅助总线的共享拆分 TDM 连接图以图 3-11 为例,以下 I2C 脚本将 U1、U2 和 U3 配置为具有主要和辅助总线的共享 TDM。

w 98 0B 00 # Set U1 Ch1 mapped to slot 0 of SDOUT

w 98 0C 01 # Set U1 Ch2 mapped to slot 1 of SDOUT

w 98 0D 02 # Set U1 Ch3 mapped to slot 2 of SDOUT

w 98 0E 03 # Set U1 Ch4 mapped to slot 3 of SDOUT

w 9A 0B 04 # Set U2 Ch1 mapped to slot 4 of SDOUT

w 9A 0C 05 # Set U2 Ch2 mapped to slot 5 of SDOUT

w 9A 22 30 # Set U2 GPIO1 as SDOUT2

w 9A 0D 40 # Set U2 Ch3 mapped to slot 0 of SDOUT2

w 9A 0E 41 # Set U2 Ch4 mapped to slot 1 of SDOUT2

w 9C 22 30 # Set U3 GPIO1 as SDOUT2

w 9C 0B 42 # Set U3 Ch1 mapped to slot 2 of SDOUT2

w 9C 0C 43 # Set U3 Ch2 mapped to slot 3 of SDOUT2

w 9C 0D 44 # Set U3 Ch3 mapped to slot 4 of SDOUT2