TIDUF05 August 2022

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

- 3Hardware, Testing Requirements, and Test Results

- 4Design and Documentation Support

- 5Documentation Support

- 6Support Resources

- 7Trademarks

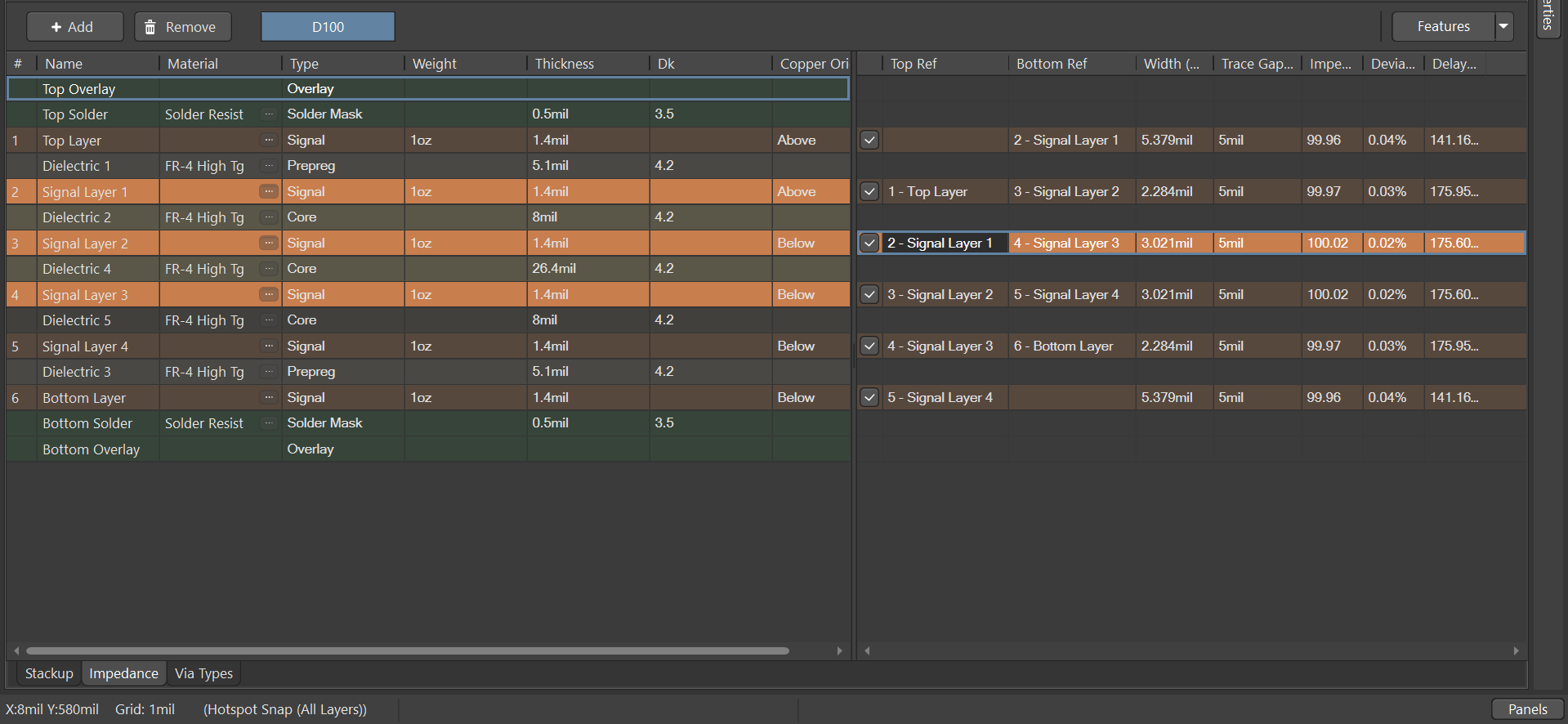

4.1.3.5 PCB Layer Stackup Recommendations

Figure 4-3 shows the 8-layer stackup used for the PMIC and serializer board. Two signal layers are required due to the complex routing requirements introduced by the small size requirements of the PCB that must include I2C, logic IOs, clock, and control signals between the PMIC, serializer, and imager. The separation of the outer layers is selected to ensure a single-ended characteristic impedance of 50 Ω, and differential characteristic impedance of 100 Ω.

In this design, high current components are placed on both the top layer and the bottom layer, so Layer 2 and Layer 7 in the stackup are dedicated ground planes to minimize high current return paths.

Figure 4-3 Layer

Stackup

Figure 4-3 Layer

Stackup