SPRUJ74 January 2023

2.2 Interfacing QP-ENET Expansion Board with J784S4XG01EVM Board

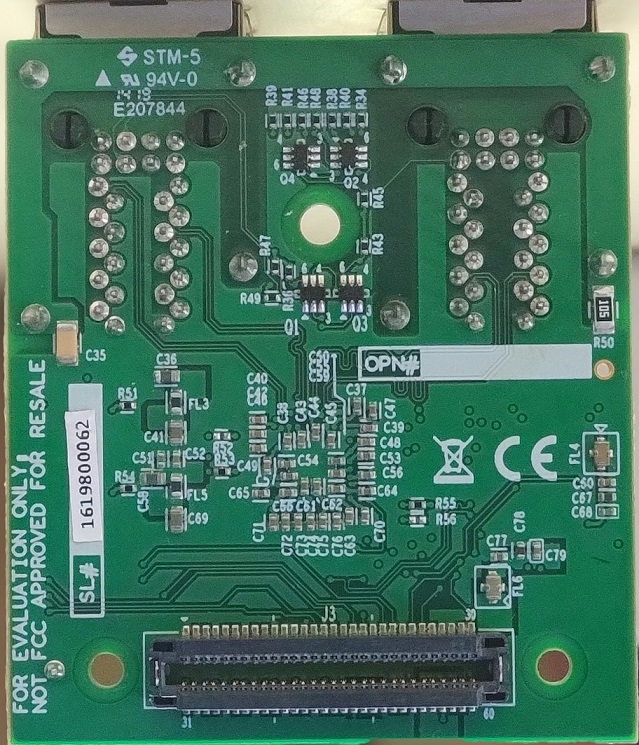

QP-ENET Expansion boards shall be interfaced with Jacinto7 J784S4XG01EVM in bottom mating configurations. The images below show the J7AHP EVM board connectors J51 and J52, which mate with the QP-ENET board as an example, with expansion connectors J3 on the QP-ENET mated to the SGMII Expansion connectors on the J7AHP EVM. It is valid to support/install on only one QP-ENET board, and in either location.

Figure 2-2 QP-ENET Expansion Board Bottom Side

Figure 2-2 QP-ENET Expansion Board Bottom Side Figure 2-3 Q/SGMII Expansion Connector on

J784S4XG01EVM Bottom Side

Figure 2-3 Q/SGMII Expansion Connector on

J784S4XG01EVM Bottom Side