SPRUJ74 January 2023

3.4.2.1 Main Clock

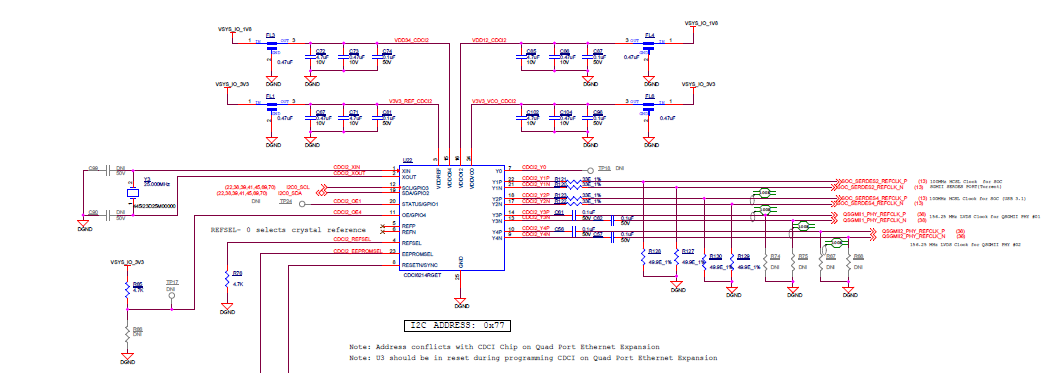

The reference clock to the PHY is generated from TI’s Clock Generator Mfr. Part Number# CDCI6214RGET, which is placed on the J7AHP EVM Board. Clock inputs are AC coupled and LVDS compliant. The clock generator can be configured by I2C0 of the J7AHP SoC. The I2C address of this clock generator is 0x77.

Figure 3-3 Default Clock Source on J7AHP EVM Board

Figure 3-3 Default Clock Source on J7AHP EVM Board