SNLA267A March 2019 – June 2019 DS90UB953-Q1 , DS90UB954-Q1 , DS90UB960-Q1

-

How to Design a FPD-Link III System Using DS90UB953-Q1 and DS90UB954-Q1

- Trademarks

- 1 Overview

- 2 Basic Design Rules

- 3 Designing the Link Between SER and DES

- 4 Designing Link Between SER and Image Sensor

- 5 Designing Link Between DES and ISP

- 6 Hardware Design

- 7

Appendix

- 7.1

Scripts

- 7.1.1 BIST Script

- 7.1.2 Example Sensor Initialization Script

- 7.1.3 CSI Enable and Port Forwarding Script

- 7.1.4 Enabling CMLOUT FPD3 RX Port 0 on 954

- 7.1.5 Remote Enabled SER GPIO Toggle Script

- 7.1.6 Local SER GPIO Toggle Script

- 7.1.7 Internal FrameSync on 953 GPIO1

- 7.1.8 External FrameSync on 953 GPIO0

- 7.1.9 SER GPIOs as Inputs and Output to DES GPIO

- 7.1.10 Pattern Generation on the 953 Script

- 7.1.11 Pattern Generation on the 954 Script

- 7.1.12 Monitor Errors for Predetermined Time Script

- 7.1.13 954 and 953 CSI Register Check Script

- 7.1.14 Time Till Lock Script on 953

- 7.2 Acknowledgments

- 7.1

Scripts

- Revision History

2.2.2 Port Selection on 954

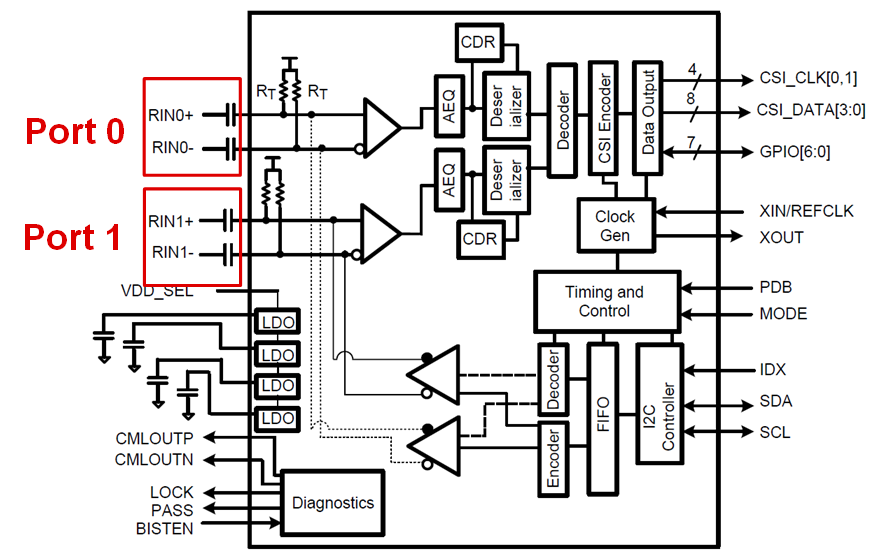

Figure 7. Illustration of Two Ports

Figure 7. Illustration of Two Ports The DS90UB954-Q1 has two ports (Port 0 and Port 1) that allow the user to interface two serializers—and subsequently, two image sensors—with one 954. As a result, the entire register space for Port 0 is similar but independent to Port 1. Therefore, the port must be accounted for when doing read or write commands to registers on the 954.

The FPD3_PORT_SEL register, with address of 0x4C, has the ability to control which port is read and which port has permission to write. Specifically, bit [4] controls which port is read where 0 indicates that read commands access port 0 and 1 indicates that read commands access port 1. Finally, bits [1] and [0] control write permissions for port 1 and port 0, respectively. Any combination of RX port registers can be written simultaneously. This is summarized in Table 8.

Broadcast mode refers to writing both to the port 0 and port 1 serializers simultaneously. This can achieved by defining both alias IDs to be the same and enabling writes to both ports.

Table 8. Bit Description of FPD3_PORT_SEL Register 0x4C

| ADDR. | 0x4C[7:5] | 0x4C[4] | 0x4C[3:2] | 0x4C[1:0] |

|---|---|---|---|---|

| Bits | 0X0 | X | 00 | XX |

| Desc. | Holds physical port number and reserved bits | Determines which port is read. | Reserved | Enables writes for Port 1 and Port 0 |