SLUAAJ7 June 2022 UCC256402 , UCC256403 , UCC256404

- Abstract

- Trademarks

- 1UCC25640x Selection Guide

- 2UCC25640x Features Brief Overview

- 3UCC25640x Power Up Guidelines and Debugging Notes

- 4References

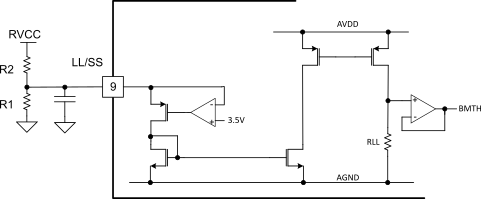

2.6.3 BMTH Generation

Figure 2-28 UCC25640x BMTH Programming

Circuit

Figure 2-28 UCC25640x BMTH Programming

Circuit- Burst mode thresholds will be programmed after startup process is finished.

- Once the startup is finished, LL/SS pin is kept constant at 3.5 V.

- Current sinks to LL/SS pin is the current mirrored flowing through an internal RLL (100kOhm) and the voltage on the RLL is nothing but BMTH.

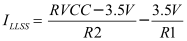

- The current flowing into the LL/SS pin is derived as Equation 9.

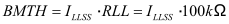

- BMTH voltage is given by Equation 10.

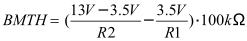

Equation 11.

Equation 11.

- Burst mode thresholds will be kept at a minimum value of 0.2 when R2 removed to limit the maximum operating switching frequency.