SLUAAJ7 June 2022 UCC256402 , UCC256403 , UCC256404

- Abstract

- Trademarks

- 1UCC25640x Selection Guide

- 2UCC25640x Features Brief Overview

- 3UCC25640x Power Up Guidelines and Debugging Notes

- 4References

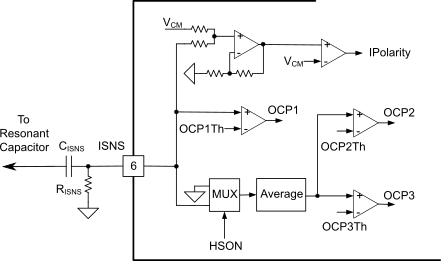

2.8.1 OCP Protection

Figure 2-33 Over

Current Protection (OCP) Protection

Figure 2-33 Over

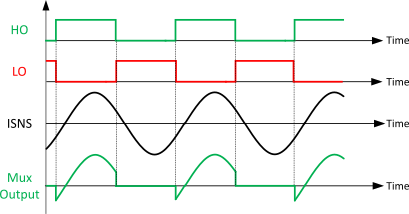

Current Protection (OCP) Protection Figure 2-34 High

Side Switch Current Extraction from ISNS Signal

Figure 2-34 High

Side Switch Current Extraction from ISNS Signal - Resonant current is reconstructed as ISNS voltage using a differentiator connected to the resonant capacitor.

- OCP1 (OCP1Th: 4 V) is for output short circuit protection; it checks the magnitude of the resonant current.

- OCP2 (OCP2Th: 0.6 V) is for over-load protection; it checks the average DC input current. The time the average input current needs to stay above OCP2 threshold before OCP2 is triggered is 2 ms.

- OCP3 (OCP3Th: 0.43 V) is also for over-load protection but it has lower threshold value compared to OCP2, OCP1; it checks the average DC input current. The time the average input current needs to stay above OCP3 threshold before OCP3 is triggered is 50 ms.

- DC input current is reconstructed by capturing the current flowing through high side MOSFET.

- Internally, ISNS voltage is truncated when HO is high and then filtered to get the average dc value.