SLUAAJ7 June 2022 UCC256402 , UCC256403 , UCC256404

- Abstract

- Trademarks

- 1UCC25640x Selection Guide

- 2UCC25640x Features Brief Overview

- 3UCC25640x Power Up Guidelines and Debugging Notes

- 4References

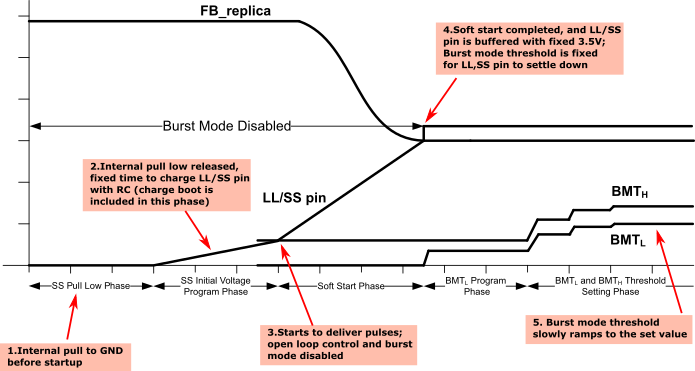

2.5.1 Soft Start Timing

- LL/SS pin capacitor determines Soft start control signal ramp rate. This would make sure initial frequency is slowly ramps down until feedback signal takes over as shown in Figure 2-14. This ramp rate helps to avoid the stress in the power stage components during the startup. Note that burst mode is disabled during the soft start which is shown in Figure 2-20

- LL/SS pin resistors and capacitor together programs the initial voltage on the pin for startup

- LL/SS pin resistors programs the burst mode high threshold.

Figure 2-20 Soft Start Timing

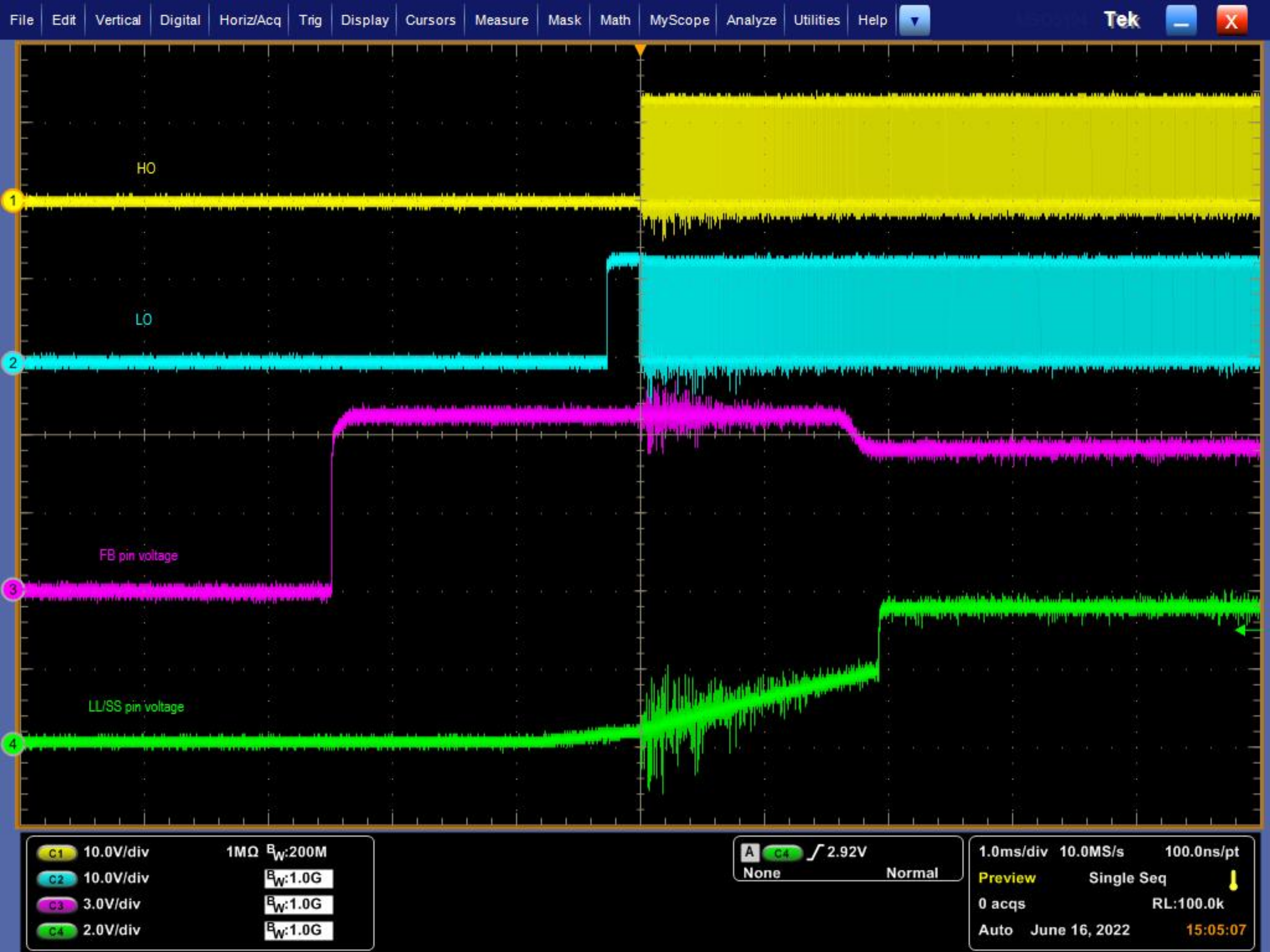

Figure 2-20 Soft Start Timing Figure 2-21 Startup waveform Ch1 – HO Ch2

– LO Ch3 – FB Ch4 – LL/SS

Figure 2-21 Startup waveform Ch1 – HO Ch2

– LO Ch3 – FB Ch4 – LL/SS