ZHCSMR1C october 2019 – september 2021 UCC5870-Q1

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Power Supplies

- 7.3.2 Driver Stage

- 7.3.3 Integrated ADC for Front-End Analog (FEA) Signal Processing

- 7.3.4 Fault and Warning Classification

- 7.3.5

Diagnostic Features

- 7.3.5.1 Undervoltage Lockout (UVLO) and Overvoltage Lockout (OVLO)

- 7.3.5.2 CLAMP, OUTH, and OUTL Clamping Circuits

- 7.3.5.3 Active Miller Clamp

- 7.3.5.4 DESAT based Short Circuit Protection (DESAT)

- 7.3.5.5 Shunt Resistor based Overcurrent Protection (OCP) and Short Circuit Protection (SCP)

- 7.3.5.6 Temperature Monitoring and Protection for the Power Transistors

- 7.3.5.7 Active High Voltage Clamping (VCECLP)

- 7.3.5.8 Two-Level Turn-Off

- 7.3.5.9 Soft Turn-Off (STO)

- 7.3.5.10 Thermal Shutdown (TSD) and Temperature Warning (TWN) of Driver IC

- 7.3.5.11 Active Short Circuit Support (ASC)

- 7.3.5.12 Shoot-Through Protection (STP)

- 7.3.5.13 Gate Voltage Monitoring and Status Feedback

- 7.3.5.14 VGTH Monitor

- 7.3.5.15 Cyclic Redundancy Check (CRC)

- 7.3.5.16 Configuration Data CRC

- 7.3.5.17 SPI Transfer Write/Read CRC

- 7.3.5.18 TRIM CRC Check

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Maps

- 8 Applications and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

7.3.5.5 Shunt Resistor based Overcurrent Protection (OCP) and Short Circuit Protection (SCP)

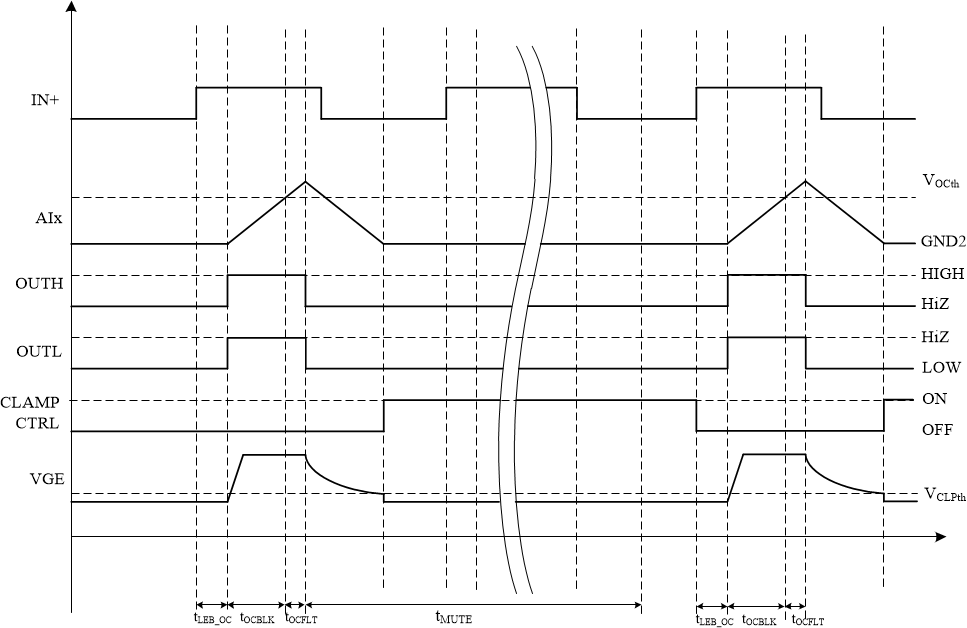

The device designates three AI* inputs (AI2, AI4, AI6) to support shunt resistor based OCP and SCP in order to support up to three power transistors in parallel. Shunt resistor based OCP/SCP protections are intended for power transistors with integrated current sense FETs. The mirrored power transistor currents is fed into a resistor, and the voltage is monitored at the AI* input. Once the voltage at the AI* input exceeds the threshold programmed using CFG6[OCTH] (for OCP, CFG6) or CFG6[SCTH] (for SCP, CFG6), the fault is indicated in the STATUS3[OC_FAULT] (for OCP, STATUS3) or the STATUS3[SC_FAULT] (for SCP, STATUS3), and if unmasked, nFLT1x is pulled low and the driver output goes to the state defined by CFG10[FS_STATE_OCP] (for OCP, CFG10) or CFG10[FS_STATE_SCP] (for SCP, CFG10). The turn-off of the driver output during a OCP or SCP fault is selectable between normal, soft turn-off (STO), or two-level turnoff (2LTO) dictated by the CFG5[2LTOFF_STO_EN] bits (CFG5). See the Soft Turn-off (STO) and Two-Level Turn-Off for additional details on STO and 2LTO, respectively. A blanking time is used for both OCP and SCP to prevent unwanted false protection triggering during transitions and is selectable in CFG6[OC_BLK] (for OCP, CFG6)) or CFG6[SC_BLK] (for SCP, CFG6)). Once the blanking time expires, any SCP/OCP fault must exist for the deglitch time before the fault is registered. Enable/disable which AI* inputs are to be used for SCP/OCP using the DOUTCFG[AI*OCSC_EN] bits (DOUTCFG). The OCP and SCP functions are enabled for the selected AI* inputs using the CFG4[OCP_DIS] (for OCP, CFG4) and CFG4[SCP_DIS] (for SCP, CFG4) bits. Please note that if AI6 is to be used for OCP/SCP, the CFG8[AI_ASC_MUX] bit (CFG8) must be configured as an ADC input. The implementation diagram and timing schemes for the shunt resistor based OCP and SCP are presented in Block diagram of implementation of shunt resistor based OCP and SCP functions and Timing scheme of implementation of shunt resistor based OCP function (safe state is LOW) respectively.

Figure 7-18 Block diagram of implementation of

shunt resistor based OCP and SCP functions.

Figure 7-18 Block diagram of implementation of

shunt resistor based OCP and SCP functions. Figure 7-19 Timing scheme of implementation of

shunt resistor based OCP function (safe state is LOW)

Figure 7-19 Timing scheme of implementation of

shunt resistor based OCP function (safe state is LOW)Current sources are available for AI2, AI4, and AI6 as open pin diagnosis tools. Enable the current sources using the CFG3[ITO2_EN] bit (CFG3). When enabled, the AI2, AI4, AI6 inputs are pulled high if left unconnected.