ZHCSMR1C october 2019 – september 2021 UCC5870-Q1

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Power Supplies

- 7.3.2 Driver Stage

- 7.3.3 Integrated ADC for Front-End Analog (FEA) Signal Processing

- 7.3.4 Fault and Warning Classification

- 7.3.5

Diagnostic Features

- 7.3.5.1 Undervoltage Lockout (UVLO) and Overvoltage Lockout (OVLO)

- 7.3.5.2 CLAMP, OUTH, and OUTL Clamping Circuits

- 7.3.5.3 Active Miller Clamp

- 7.3.5.4 DESAT based Short Circuit Protection (DESAT)

- 7.3.5.5 Shunt Resistor based Overcurrent Protection (OCP) and Short Circuit Protection (SCP)

- 7.3.5.6 Temperature Monitoring and Protection for the Power Transistors

- 7.3.5.7 Active High Voltage Clamping (VCECLP)

- 7.3.5.8 Two-Level Turn-Off

- 7.3.5.9 Soft Turn-Off (STO)

- 7.3.5.10 Thermal Shutdown (TSD) and Temperature Warning (TWN) of Driver IC

- 7.3.5.11 Active Short Circuit Support (ASC)

- 7.3.5.12 Shoot-Through Protection (STP)

- 7.3.5.13 Gate Voltage Monitoring and Status Feedback

- 7.3.5.14 VGTH Monitor

- 7.3.5.15 Cyclic Redundancy Check (CRC)

- 7.3.5.16 Configuration Data CRC

- 7.3.5.17 SPI Transfer Write/Read CRC

- 7.3.5.18 TRIM CRC Check

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Maps

- 8 Applications and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

8.3.1.1 DESAT Input

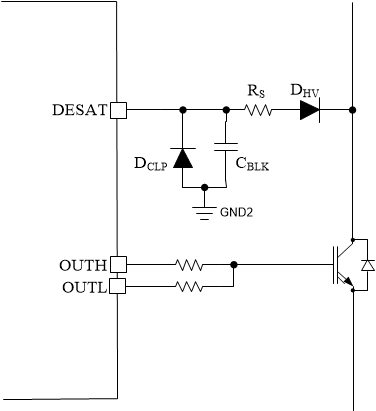

The DESAT circuit monitors the power module (IGBT for example) for short circuit or over current protection. The external circuit includes four components (Figure 8-8): blanking capacitor (CBLK), clamping diode (DCLP), series resistor RS and high-voltage blocking diode (DHV). CBLK is used to determine the blanking time, tBLK. The time period for tBLK must be long enough to prevent a false trigger when the during the normal operation turn-on cycle. tBLK is calculated as:

The high voltage diode DHV blocks the high voltage (VCE) while IGBT is OFF. The voltage rating for DHV must be higher than the DC bus voltage plus any switching transient voltage. It is good practice to choose a voltage rating for DHV to be the same or higher than the IGBT voltage rating. Once the proper voltage rating is determined, choose a diode with the least amount of junction capacitance to prevent coupling of DESAT with the dV/dt of the VCE switching. Clamping diode, DCLP, provides a current path to for any coupling current due to the aforementioned junction capacitance of DHV. Select a diode large enough to handle any expected coupling current. The series resistor, RS, dampens any oscillations in the DESAT loop and determines the actual DESAT detection VCE voltage. The actual threshold is calculated as:

VDHV is the forward voltage drop of the DHV diode and ICHG is the blanking capacitor charging current selected using the CFG5[DESAT_CHG_CURR] bits.

Figure 8-8 External Components for DESAT

Figure 8-8 External Components for DESAT