ZHCSQV9A August 2022 – April 2024 TMDS1204

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

-

7 Detailed Description

- 7.1 Functional Block Diagram

- 7.2

Feature Description

- 7.2.1 4-Level Inputs

- 7.2.2 I/O Voltage Level Selection

- 7.2.3 HPD_OUT

- 7.2.4 Lane Control

- 7.2.5 Swap

- 7.2.6 Linear and Limited Redriver

- 7.2.7 Main Link Inputs

- 7.2.8 Receiver Equalizer

- 7.2.9 CTLE Bypass

- 7.2.10 Adaptive Equalization in HDMI 2.1 FRL

- 7.2.11 HDMI 2.1 Link Training Compatible Rx EQ

- 7.2.12 Input Signal Detect

- 7.2.13 Main Link Outputs

- 7.2.14 HDMI DDC Capacitance

- 7.2.15 DisplayPort

- 7.3 Device Functional Modes

- 7.4 Programming

- 7.5 Register Maps

- 8 Application and Implementation

- 9 器件和文档支持

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

8.2.3 Application Curves

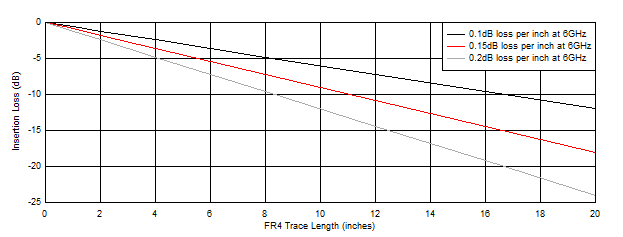

Figure 8-3 FR4

Trace Insertion Loss at 6GHz

Figure 8-3 FR4

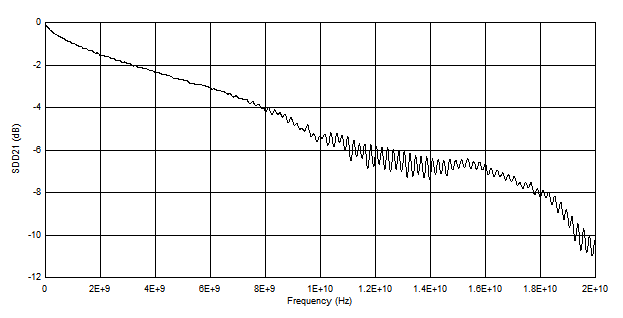

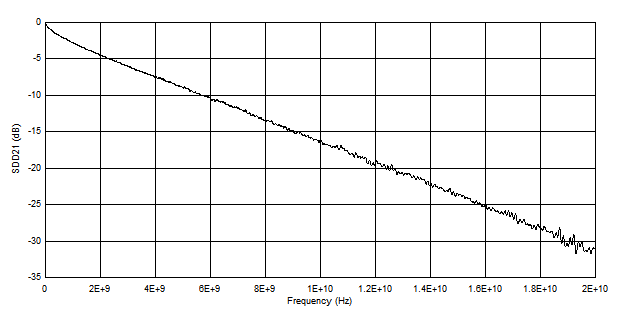

Trace Insertion Loss at 6GHz Figure 8-5 Post-Channel Insertion Loss at TTP4

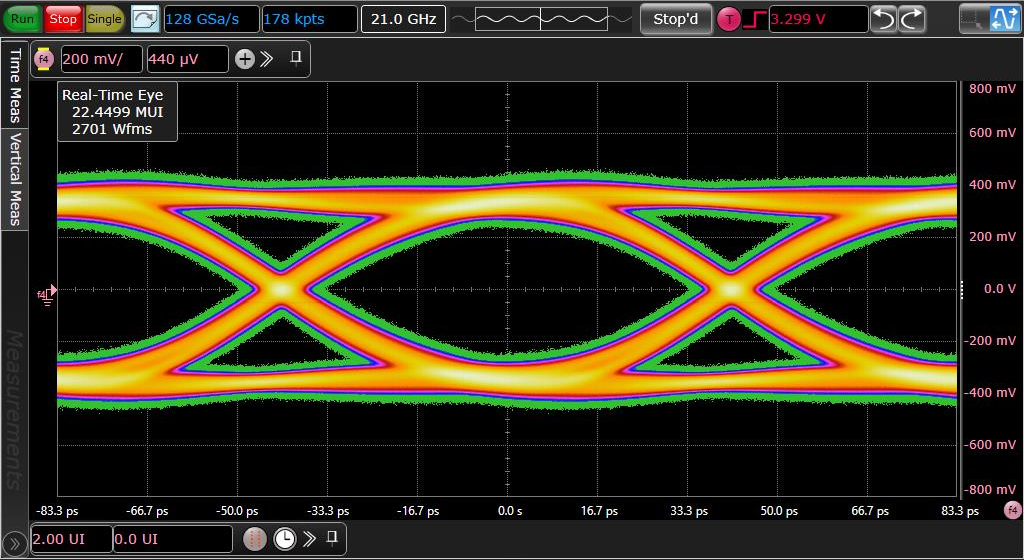

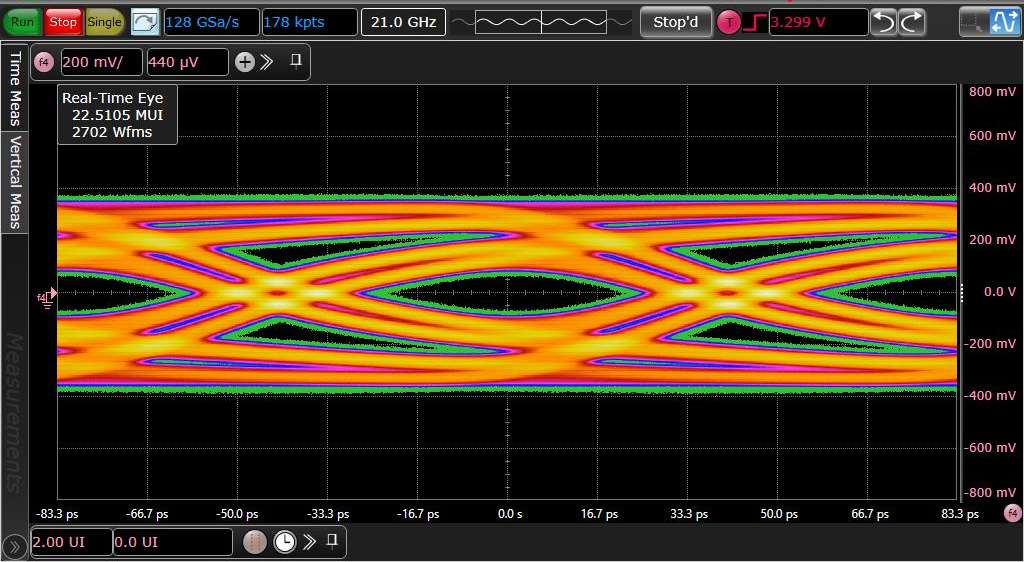

Figure 8-5 Post-Channel Insertion Loss at TTP4 Figure 8-7 12Gbps Output Eye at TTP4 After Pre and Post Channels

Figure 8-7 12Gbps Output Eye at TTP4 After Pre and Post Channels Figure 8-4 Pre-Channel Insertion Loss at TTP2

Figure 8-4 Pre-Channel Insertion Loss at TTP2 Figure 8-6 12Gbps Input Eye at TTP2 After Pre-channel

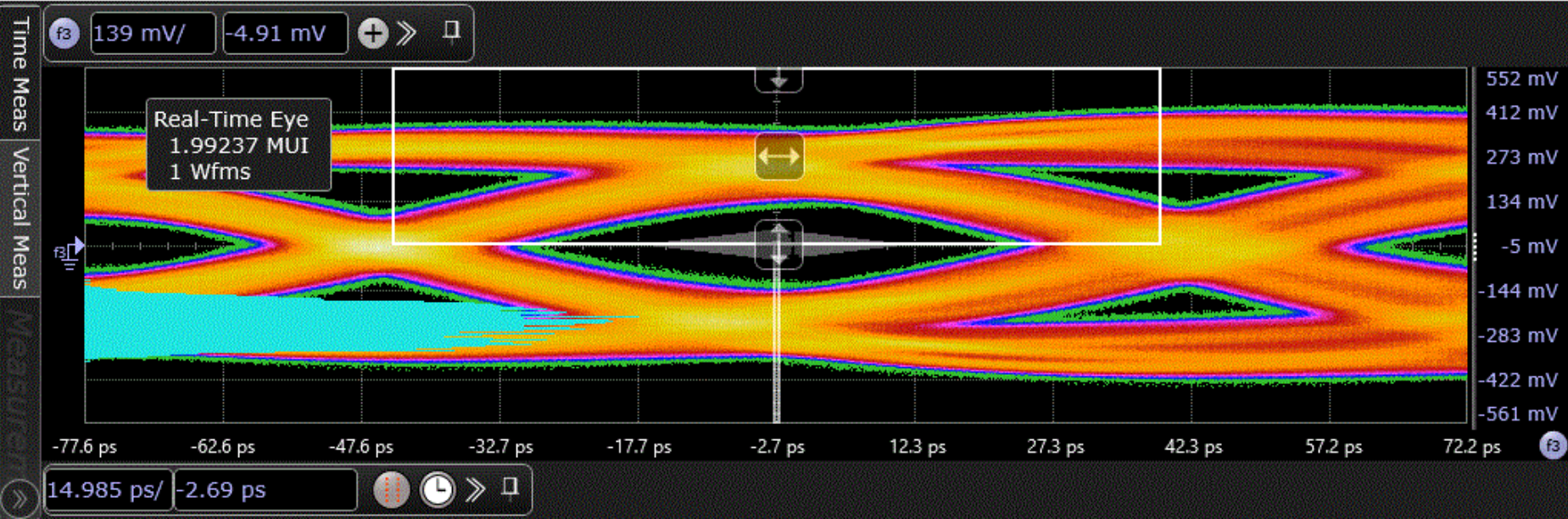

Figure 8-6 12Gbps Input Eye at TTP2 After Pre-channel Figure 8-8 12Gbps Output Eye at TTP4_EQ After Pre and Post Channels

Figure 8-8 12Gbps Output Eye at TTP4_EQ After Pre and Post Channels