ZHCSKF4C March 2017 – October 2019 LMH1228

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 4-Level Input Pins and Thresholds

- 7.3.2 OUT0_SEL and SDI_OUT2_SEL Control

- 7.3.3 Input Signal Detect

- 7.3.4 Continuous Time Linear Equalizer (CTLE)

- 7.3.5 Clock and Data (CDR) Recovery

- 7.3.6 Internal Eye Opening Monitor (EOM)

- 7.3.7 Output Function Control

- 7.3.8 Output Driver Control

- 7.3.9 Status Indicators and Interrupts

- 7.4 Device Functional Modes

- 7.5 Register Maps

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

8.2.2.3 Application Curves

The LMH1228 performance on OUT0± was measured with the test setup shown in Figure 22.

Figure 35. Test Setup for LMH1228 to OUT0±

Figure 35. Test Setup for LMH1228 to OUT0± The eye diagrams in this subsection show how the LMH1228 improves overall signal integrity in the data path for 100-Ω differential FR4 PCB trace at IN0±.

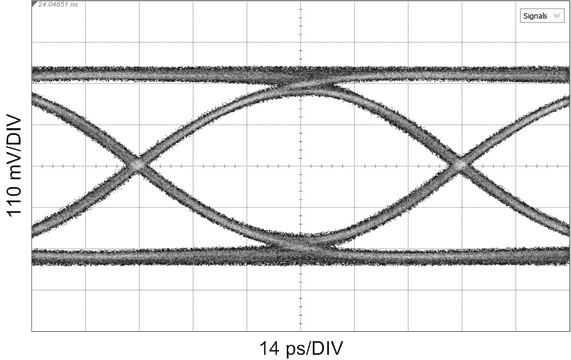

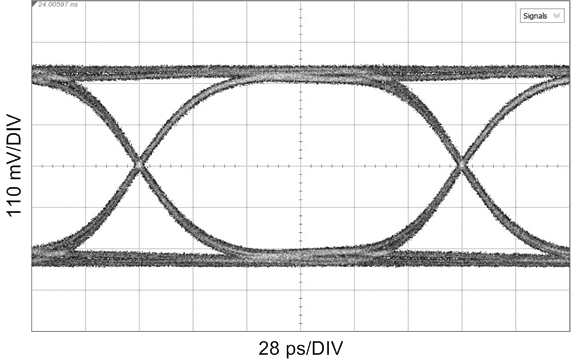

Measured at OUT0±

HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F

Figure 36. 11.88 Gbps, TL = 20" FR4, Reclocked HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F

Measured at OUT0±

HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F

Figure 38. 2.97 Gbps, TL = 20" FR4, Reclocked HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F

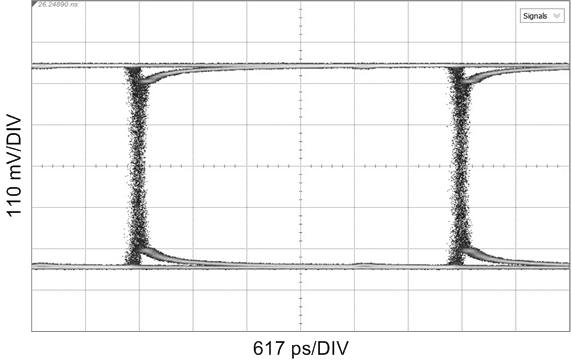

Measured at OUT0±

HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F

Figure 40. 270 Mbps, TL = 20" FR4, Reclocked HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F

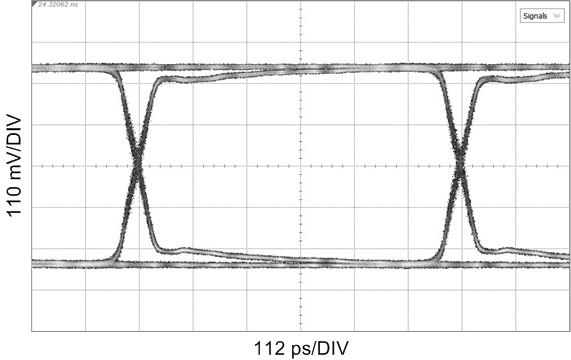

Measured at OUT0±

HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F

Figure 37. 5.94 Gbps, TL = 20" FR4, Reclocked HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F

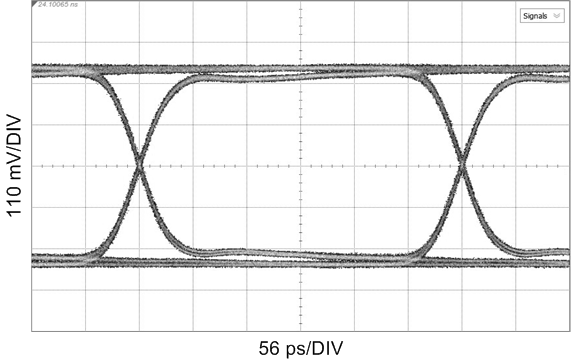

Measured at OUT0±

HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F

Figure 39. 1.485 Gbps, TL = 20" FR4, Reclocked HOST_EQ0 = F, SDI_OUT2_SEL = L, OUT_CTRL = F