ZHCU942 January 2024

2.3.2 FPGA DDR2 SDRAM 接口布线

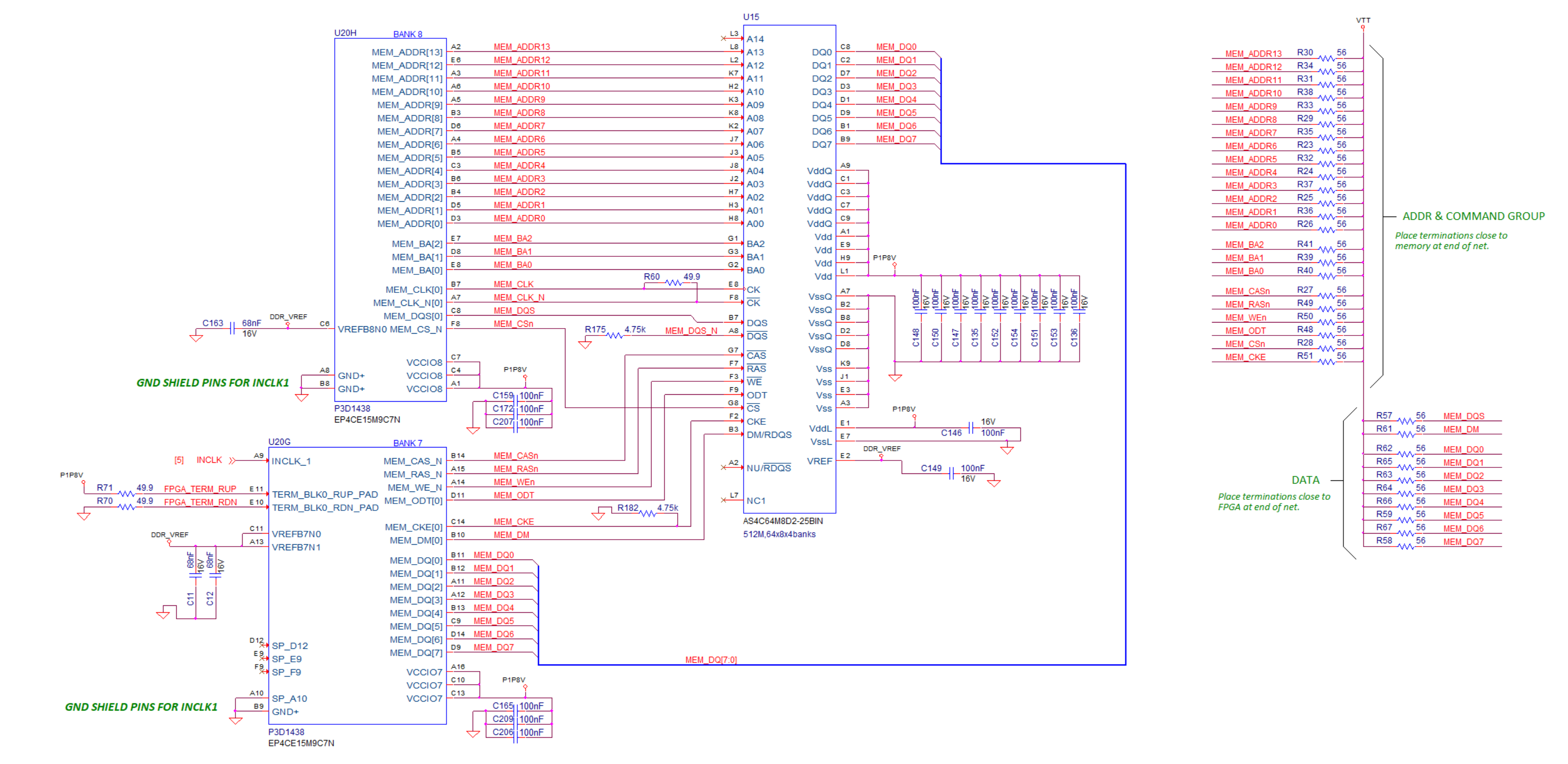

FPGA 至 DDR2 SDRAM 接口基于 400MHz DDR 时钟速率。图 2-3 展示了 Intel® Cyclone® IV E FPGA (EP4CE15M9C7N) 至 Alliance DDR2 SDRAM (AS4C64M8D2-25BIN) 的接口图,而表 2-5 中定义了推荐的接口布局指南。

图 2-3 FPGA-DDR2 接口

图 2-3 FPGA-DDR2 接口表 2-5 建议的 FPGA-DDR2 PCB 匹配和布线延迟

| GROUP | 组名称 | 组内的长度匹配 | 与其他信号的长度匹配 | 额外的布线要求 |

|---|---|---|---|---|

| MEM_ADDR[13:0]、MEM_BA[2:0]、MEM_CASn、MEM_RASn、MEM_WEn、MEM_ODT MEM_CKE、MEM_CSn | 地址/控制组 | 组内 ±50ps | 比 MEM_CLK 和 MEM_CLK_N 低 0ps 至 15ps | 50Ω - 将终端放置在布线的 DDR2 末端 - 最大长度 250ps - 最小长度 200ps |

| MEM_DQ[7:0]、MEM_DM、MEM_DQS | 数据组 | 组内 ±10ps | MEM_CLK、MEM_CLK_N ±10ps | 50Ω - 使用内层 - 在同一层上布线 - 将终端放置在布线的 FPGA 末端 - 最大长度 250ps - 最小长度 200ps |

| MEM_CLK、MEM_CLK_N | CLK 组 | 组内 ±2ps | MEM_DQS ±2ps 必须比 ADDR 和 CNTL 组长 0ps 至 15ps | 100 差分 - 尽量缩短外层上的布线 - 使用内层 - 最大长度 250ps - 最小长度 200ps |

PCB 布线最佳做法:

- 尽可能使用 PCB 内层

- 在同一层上布线 DDR_DQ(7:0)、MEM_DM 和 DDR_DQS