ZHCAED7B August 2024 – May 2025 LMK6C

4.2 实验室测量结果以及与仿真数据的相关性

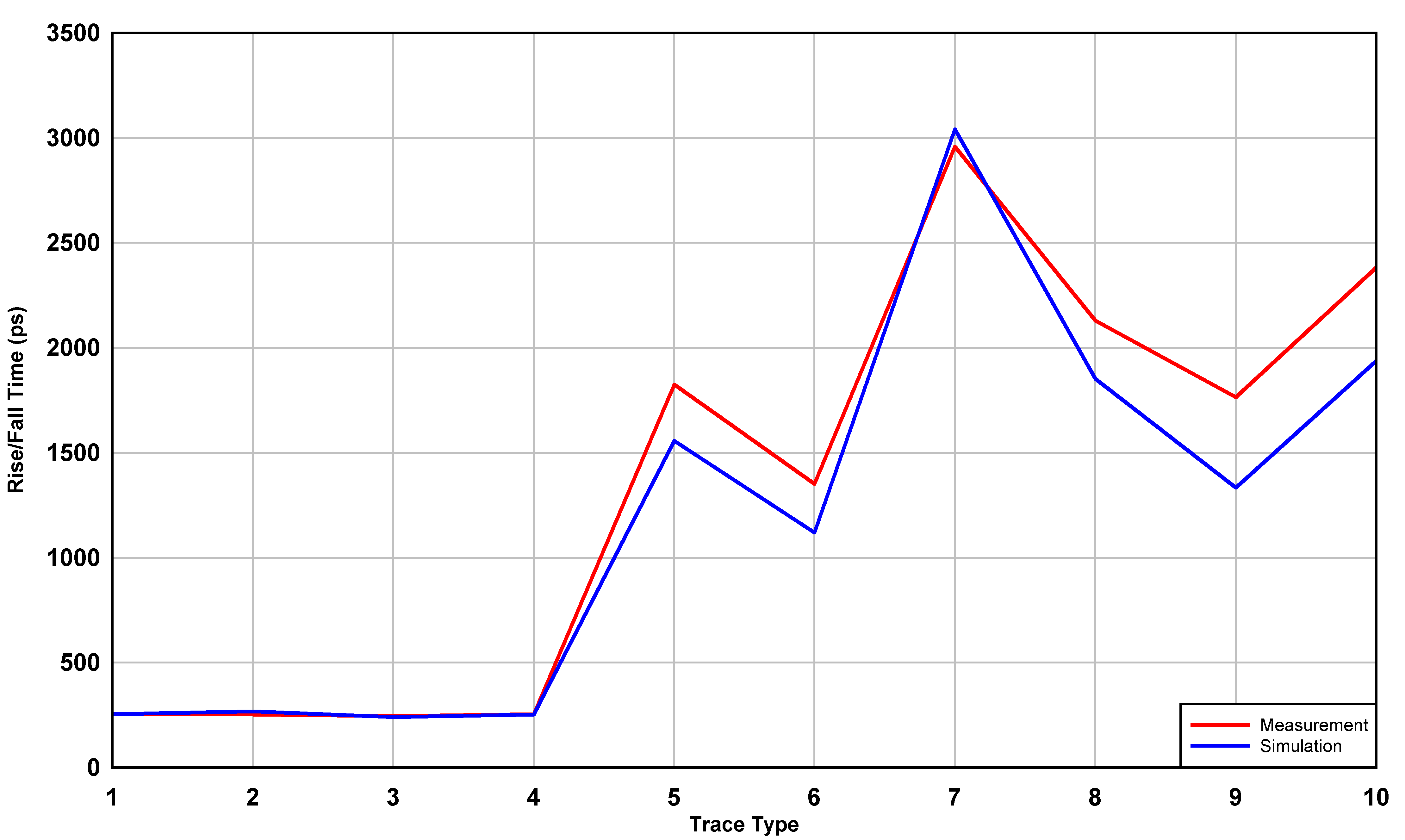

在每个输出端的负载电容为 2pF 的情况下,按照 节 2 中所述的程序提取电路板布局参数,并在 Hyperlynx 中运行信号完整性仿真。使用此电路板收集的测量结果以及与基于仿真结果的预测值的比较如下所示。

表 4-1 多负载板上,不同布线拓扑的上升或下降时间和抖动结果

| 跟踪类型 | 跟踪说明 | 抖动 (fs) 测量 | 上升时间 (ps) 测量 | 下降时间 (ps) 测量 | 上升时间 (ps) 仿真 | 下降时间 (ps) 仿真 |

|---|---|---|---|---|---|---|

| 1 | 2 英寸单线路,含 1 个过孔 | 335 | 250 | 263 | 263 | 245 |

| 2 | 2 英寸单线路,含 2 个过孔 | 335 | 249 | 257 | 270 | 266 |

| 3 | 1 英寸单线路,无过孔 | 333 | 238 | 254 | 277 | 204 |

| 4 | 2 英寸单线路,无过孔 | 334 | 251 | 259 | 263 | 244 |

| 5 | 2 英寸双线路,在驱动器附近拆分 | 336 | 1780 | 1870 | 1475 | 1640 |

| 6 | 2 英寸双线路,在负载附近拆分 | 332 | 1283 | 1422 | 1050 | 1190 |

| 7 | 2 英寸三线路,在驱动器附近拆分 | 350 | 2895 | 3023 | 2904 | 3180 |

| 8 | 2 英寸三线路,在负载附近拆分 | 350 | 2051 | 2210 | 1715 | 1990 |

| 9 | 1.5 英寸三线路,在负载附近拆分 | 349 | 1693 | 1837 | 1248 | 1420 |

| 10 | 1.6 英寸四线路,在负载附近拆分 | 376 | 2385 | 2380 | 1796 | 2080 |

从 表 4-1 中显示的结果可以看出,布线拓扑几乎不会影响抖动性能。请注意,抖动测量是用包含内部 50Ω 终端的相位噪声分析仪进行的,与高阻抗纯电容负载相比,它可以减少在接收器处测得的反射。仿真测量结果的上升/下降时间趋势与实验室测量结果密切相关。图 4-2 中 x 轴的布线编号与 表 4-1 中使用的编号方案和 图 4-1 上的标签相对应。随着布线扇出的增加,仿真结果的耦合度与实验室测量结果相比降低。这主要是因为未在测试设置中对 SMA 适配器、电缆和探头的寄生电容进行建模。根据实验室测量结果与仿真数据之间的相关性,预计仿真上升/下降时间结果与实际测量结果的裕度在 ±25% 的范围内。此裕度考虑了器件间差异、影响寄生电容和特性布线阻抗的 PCB 覆铜厚度制造容差以及其他环境因素。总而言之,驱动多个负载时,系统设计人员可以放心地使用 IBIS 仿真为不同布线方案估算时钟信号的上升/下降时间和信号完整性。

在所有布线拓扑中,当负载为 2pF 时,输出振幅保持轨到轨的规定范围内,但会随着负载数量或总负载电容的增加而降低。在仿真和实际实验室测量中,在负载附近进行拆分(星型线路拓扑)布线可实现更好的性能。

图 4-2 仿真与测量:多负载板上,不同布线拓扑的平均上升或下降时间结果

图 4-2 仿真与测量:多负载板上,不同布线拓扑的平均上升或下降时间结果