ZHCABB2 June 2021 DRA821U , DRA821U-Q1 , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4VM , TDA4VM-Q1

6.1 示例

在为系统进行定制时,应查看存储器映射以确定必须保护的任何区域,并查看应保护的存储器区域。如果 A72 不需要访问权限,则可以有选择性地对该存储器设置防火墙。

参考来自 Processor SDK QNX 7.1 的系统存储器映射,可以生成 表 6-1。在该表中,可以查看存储器区域以识别对防火墙有意义的存储器范围,防止 A72 访问。

有了这些防火墙,所有 Vision Apps SDK 演示都将继续运行。如果 A72 软件无意中试图访问任何受防火墙保护的存储器区域,则会发生异常。

表 6-1 用于识别存储器范围的存储器区域

| 名称 | 起始地址 | 结束地址 | 大小 | 属性 | 说明 |

|---|---|---|---|---|---|

| L2RAM_C66x_1 | 0x00800000 | 0x00837FFF | 224.00 KB | RWIX | L2 for C66x_1 |

| L2RAM_C66x_2 | 0x00800000 | 0x00837FFF | 224.00 KB | RWIX | L2 for C66x_2 |

| MAIN_OCRAM_ MCU2_0 |

0x03600000 | 0x0361FFFF | 128.00 KB | RWIX | Main OCRAM for MCU2_0 |

| MAIN_OCRAM_ MCU2_1 |

0x03620000 | 0x0363FFFF | 128.00 KB | RWIX | Main OCRAM for MCU2_1 |

| L2RAM_C7x_1 | 0x64800000 | 0x64877FFF | 480.00 KB | RWIX | L2 for C7x_1 |

| L1RAM_C7x_1 | 0x64E00000 | 0x64E03FFF | 16.00 KB | RWIX | L1 for C7x_1 |

| MSMC_MPU1 | 0x70000000 | 0x7001FFFF | 128.00 KB | RWIX | MSMC reserved for MPU1 for ATF |

| MSMC_C7x_1 | 0x70020000 | 0x707E7FFF | 7.78 MB | RWIX | MSMC for C7x_1 |

| MSMC_DMSC | 0x707F0000 | 0x707FFFFF | 64.00 KB | RWIX | MSMC reserved for DMSC IPC |

| DDR_MCU1_0_IPC | 0xA0000000 | 0xA00FFFFF | 1024.00 KB | RWIX | DDR for MCU1_0 for Linux IPC |

| DDR_MCU1_0_ RESOURCE_TABLE |

0xA0100000 | 0xA01003FF | 1024 B | RWIX | DDR for MCU1_0 for Linux resource table |

| DDR_MCU1_0 | 0xA0100400 | 0xA0FFFFFF | 15.00 MB | RWIX | DDR for MCU1_0 for code/data |

| DDR_MCU2_0_IPC | 0xA1000000 | 0xA10FFFFF | 1024.00 KB | RWIX | DDR for MCU2_0 for Linux IPC |

| DDR_MCU2_0_ RESOURCE_TABLE |

0xA1100000 | 0xA11003FF | 1024 B | RWIX | DDR for MCU2_0 for Linux resource table |

| DDR_MCU2_0 | 0xA1100400 | 0xA2FFFFFF | 31.00 MB | RWIX | DDR for MCU2_0 for code/data |

| DDR_MCU2_1_IPC | 0xA3000000 | 0xA30FFFFF | 1024.00 KB | RWIX | DDR for MCU2_1 for Linux IPC |

| DDR_MCU2_1_ RESOURCE_TABLE |

0xA3100000 | 0xA31003FF | 1024 B | RWIX | DDR for MCU2_1 for Linux resource table |

| DDR_MCU2_1 | 0xA3100400 | 0xA4FFFFFF | 31.00 MB | RWIX | DDR for MCU2_1 for code/data |

| DDR_MCU3_0_IPC | 0xA5000000 | 0xA50FFFFF | 1024.00 KB | RWIX | DDR for MCU3_0 for Linux IPC |

| DDR_MCU3_0_ RESOURCE_TABLE |

0xA5100000 | 0xA51003FF | 1024 B | RWIX | DDR for MCU3_0 for Linux resource table |

| DDR_MCU3_0 | 0xA5100400 | 0xA57FFFFF | 7.00 MB | RWIX | DDR for MCU3_0 for code/data |

| DDR_MCU3_1_IPC | 0xA5800000 | 0xA58FFFFF | 1024.00 KB | RWIX | DDR for MCU3_1 for Linux IPC |

| DDR_MCU3_1_ RESOURCE_TABLE |

0xA5900000 | 0xA59003FF | 1024 B | RWIX | DDR for MCU3_1 for Linux resource table |

| DDR_MCU3_1 | 0xA5900400 | 0xA5FFFFFF | 7.00 MB | RWIX | DDR for MCU3_1 for code/data |

| DDR_C66x_2_IPC | 0xA6000000 | 0xA60FFFFF | 1024.00 KB | RWIX | DDR for C66x_2 for Linux IPC |

| DDR_C66x_1_ RESOURCE_TABLE |

0xA6100000 | 0xA61003FF | 1024 B | RWIX | DDR for C66x_1 for Linux resource table |

| DDR_C66x_1_BOOT | 0xA6200000 | 0xA62003FF | 1024 B | RWIX | DDR for C66x_1 for boot section |

| DDR_C66x_1 | 0xA6200400 | 0xA6FFFFFF | 14.00 MB | RWIX | DDR for C66x_1 for code/data |

| DDR_C66x_1_IPC | 0xA7000000 | 0xA70FFFFF | 1024.00 KB | RWIX | DDR for C66x_1 for Linux IPC |

| DDR_C66x_2_ RESOURCE_TABLE |

0xA7100000 | 0xA71003FF | 1024 B | RWIX | DDR for C66x_2 for Linux resource table |

| DDR_C66x_2_BOOT | 0xA7200000 | 0xA72003FF | 1024 B | RWIX | DDR for C66x_2 for boot section |

| DDR_C66x_2 | 0xA7200400 | 0xA7FFFFFF | 14.00 MB | RWIX | DDR for C66x_2 for code/data |

| DDR_C7x_1_IPC | 0xA8000000 | 0xA80FFFFF | 1024.00 KB | RWIX | DDR for C7x_1 for Linux IPC |

| DDR_C7x_1_ RESOURCE_TABLE |

0xA8100000 | 0xA81003FF | 1024 B | RWIX | DDR for C7x_1 for Linux resource table |

| DDR_C7x_1_BOOT | 0xA8200000 | 0xA82003FF | 1024 B | RWIX | DDR for C7x_1 for boot section |

| DDR_C7x_1_VECS | 0xA8400000 | 0xA8403FFF | 16.00 KB | RWIX | DDR for C7x_1 for vecs section |

| DDR_C7x_1_ SECURE_VECS |

0xA8600000 | 0xA8603FFF | 16.00 KB | RWIX | DDR for C7x_1 for secure vecs section |

| DDR_C7x_1 | 0xA8604000 | 0xA8FFFFFF | 9.98 MB | RWIX | DDR for C7x_1 for code/data |

| IPC_VRING_MEM | 0xAA000000 | 0xABFFFFFF | 32.00 MB | Memory for IPC Vring's.MUST be non-cached or cache-coherent | |

| APP_LOG_MEM | 0xAC000000 | 0xAC03FFFF | 256.00 KB | Memory for remote core logging | |

| TIOVX_OBJ_ DESC_MEM |

0xAC040000 | 0xADFDFFFF | 31.62 MB | Memory for TI OpenVX shared memory.MUST be non-cached or cache-coherent | |

| PCIE_QUEUE_ SHARED_MEM |

0xADFE0000 | 0xADFEFFFF | 64.00 KB | Memory for IPC over PCIe using shared memory.MUST be non-cached or cache-coherent | |

| PCIE_QUEUE_ MIRROR_REMOTE_ SHARED_MEM |

0xADFF0000 | 0xADFFFFFF | 64.00 KB | Reserved Memory for RAT mapping of remote PCIe IPC shared memory.MUST be non-cached or cache-coherent | |

| DDR_SHARED_MEM | 0xAE000000 | 0xCDFFFFFF | 512.00 MB | Memory for shared memory buffers in DDR | |

| DDR_MCU2_0_ NON_CACHE |

0xCE000000 | 0xCE00FFFF | 64.00 KB | RWIX | DDR for MCU2_0 for non-cached heap |

| DDR_MCU2_1_ NON_CACHE |

0xCE010000 | 0xD1FFFFFF | 63.94 MB | RWIX | DDR for MCU2_1 for non-cached heap |

| DDR_MCU1_0_ LOCAL_HEAP |

0xD2000000 | 0xD21FFFFF | 2.00 MB | RWIX | DDR for MCU1_0 for local heap |

| DDR_MCU1_1_ LOCAL_HEAP |

0xD2200000 | 0xD23FFFFF | 2.00 MB | RWIX | DDR for MCU1_1 for local heap |

| DDR_MCU2_0_ LOCAL_HEAP |

0xD2400000 | 0xD2BFFFFF | 8.00 MB | RWIX | DDR for MCU2_0 for local heap |

| DDR_MCU2_1_ LOCAL_HEAP |

0xD2C00000 | 0xD3BFFFFF | 16.00 MB | RWIX | DDR for MCU2_1 for local heap |

| DDR_MCU3_0_ LOCAL_HEAP |

0xD3C00000 | 0xD3DFFFFF | 2.00 MB | RWIX | DDR for MCU3_0 for local heap |

| DDR_MCU3_1_ LOCAL_HEAP |

0xD3E00000 | 0xD3FFFFFF | 2.00 MB | RWIX | DDR for MCU3_1 for local heap |

| DDR_C66X_1_ LOCAL_HEAP |

0xD4000000 | 0xD4FFFFFF | 16.00 MB | RWIX | DDR for c66x_1 for local heap |

| DDR_C66X_1_ SCRATCH |

0xD5000000 | 0xD7FFFFFF | 48.00 MB | RWIX | DDR for c66x_1 for Scratch Memory |

| DDR_C66X_2_ LOCAL_HEAP |

0xD8000000 | 0xD8FFFFFF | 16.00 MB | RWIX | DDR for c66x_2 for local heap |

| DDR_C66X_2_ SCRATCH |

0xD9000000 | 0xDBFFFFFF | 48.00 MB | RWIX | DDR for c66x_2 for Scratch Memory |

| DDR_C7X_1_ LOCAL_HEAP |

0xDC000000 | 0xEBFFFFFF | 256.00 MB | RWIX | DDR for c7x_1 for local heap |

| DDR_C7X_1_ SCRATCH |

0xEC000000 | 0xF9FFFFFF | 224.00 MB | RWIX | DDR for c7x_1 for Scratch Memory |

| TIOVX_LOG_ RT_MEM |

0xFA000000 | 0xFAFFFFFF | 16.00 MB | Memory for TI OpenVX shared memory for Run-time logging.MUST be non-cached or cache-coherent | |

| DDR_MCU1_1_IPC | 0xFB000000 | 0xFB0FFFFF | 1024.00 KB | RWIX | DDR for MCU1_1 for Linux IPC |

| DDR_MCU1_1_ RESOURCE_TABLE |

0xFB100000 | 0xFB1003FF | 1024 B | RWIX | DDR for MCU1_1 for Linux resource table |

| DDR_MCU1_1 | 0xFB100400 | 0xFBFFFFFF | 15.00 MB | RWIX | DDR for MCU1_1 for code/data |

使用该表并结合要设置防火墙保护的相邻存储器区域,以下 2 个 DDR 范围涵盖了 A72 不应访问的所有存储器位置。

| 起始地址 | 终止地址 |

|---|---|

| 0XA0000000 | 0XA8FFFFFF |

| 0xCE000000 | 0xFBFFFFFF |

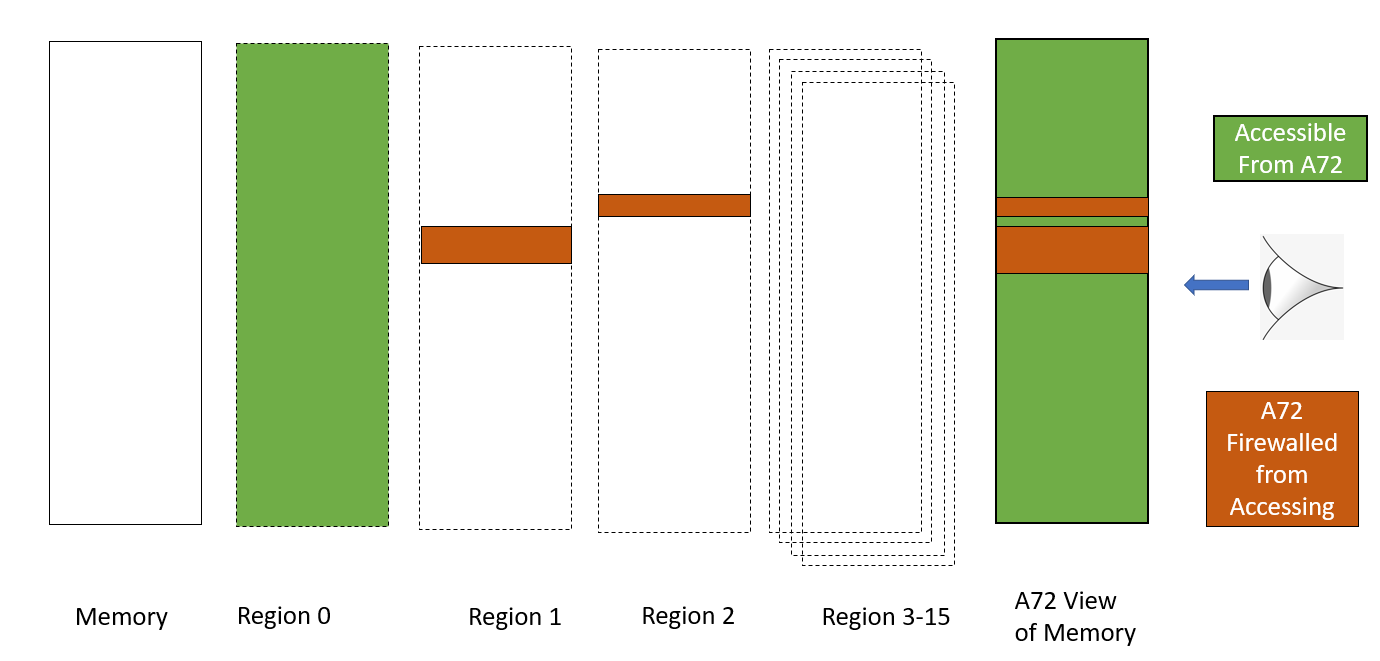

若要防止 A72 访问这两个存储器范围,必须为每个存储器配置一个防火墙区域,并将区域权限指定为不允许任何 A72 访问。在以下示例代码中,A72 主防火墙的区域 0 设置为允许来自 A72 的所有访问,而区域 1 和区域 2 设置为防止 A72 访问需要设置防火墙保护的存储器范围。从 A72 的角度来看,可访问存储器的结果视图如下图所示。

图 6-1 示例代码

图 6-1 示例代码