ZHCAB39E January 2022 – February 2022 TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S

4.3.2 Abs2Qep 停止锁存器

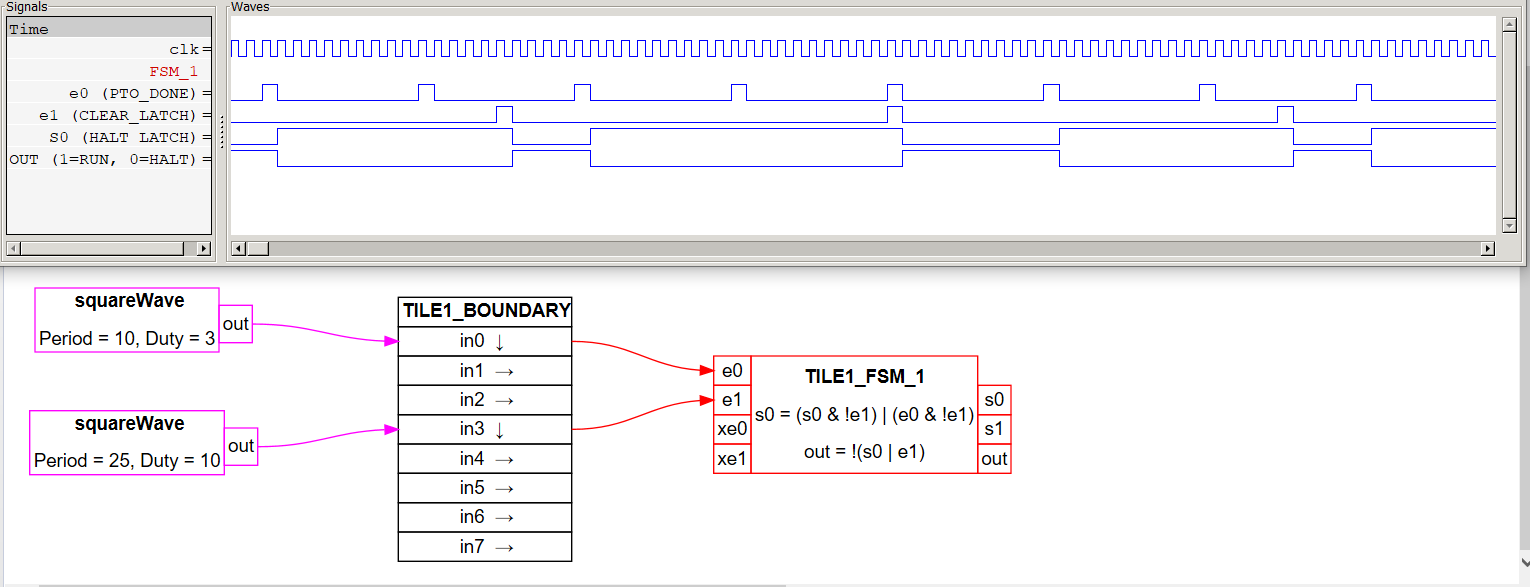

HALT_LATCH 和 RUN/HALT 输出是使用有限状态机实现的。输出信号连接到产生 QCLK 的计数器 mode0 输入端。RUN/HALT 输出仅取决于锁存器的当前状态以及来自 CPU 的 HALT 信号。如果 HALT 信号为低电平且未设置锁存器,则将生成 QCLK (COUNTER mode0 = out = 1)。在所有其他情况下,不会生成 QCLK (COUNTER mode0 = out = 0)。这将表示为 out = !(s0 | e1)。

表 4-6 RUN/HALT 输出

| s0 (LATCH) |

e1 (HALT/CLEAR LATCH) |

out = !(s0|e1) | QCLK 生成 |

|---|---|---|---|

| 0 | 0 | 1 | 运行 |

| 0 | 1 | 0 | 停止 |

| 1 | 0 | 0 | 停止 |

| 1 | 1 | 0 | 停止 |

HALT_LATCH 是在 PTO_DONE 的上升沿设置的。该设置状态将保持,直到 CPU 发出的 HALT/CLEAR_LATCH 信号的上升沿将状态清除为止。

表 4-7 HALT_LATCH 卡诺图

| PTO_DONE、CLEAR_LATCH(e0、e1) | |||||

| 00 | 01 | 11 | 10 | ||

| s0 (LATCH) |

0 | 0 | 0 | 0 | 1 (2) |

| 1 | 1 (1) | 0 | 0 | 1 (1)、(2) | |

(1) s0_1 = s0 & !e1

(2) s0_2 = e0 & !e1

图 4-10 中显示了停止锁存器的 SystemC 仿真。

图 4-10 停止锁存器的仿真

图 4-10 停止锁存器的仿真