TIDT308 October 2022

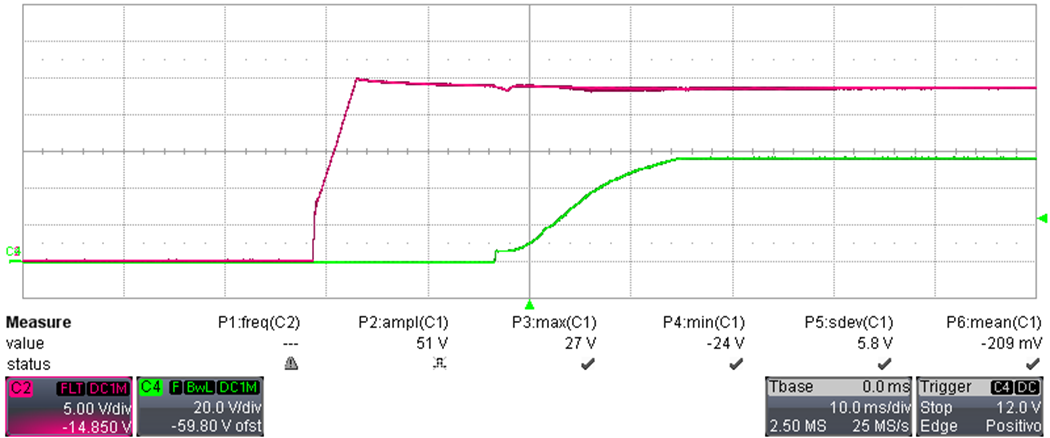

3.4.1 Full Load

Figure 3-7 Start-Up With Full

Load

Figure 3-7 Start-Up With Full

Load- Channel C2: Input voltage (5 V /div, 10 ms / div, DC coupling, 20-MHz BWL)

- Channel C4: Output voltage (20 V/div, DC coupling, 20-MHz BWL)

TIDT308 October 2022

Figure 3-7 Start-Up With Full

Load

Figure 3-7 Start-Up With Full

Load