SNLA415 August 2022 DS160PT801

6.1 Phase 0 and 1

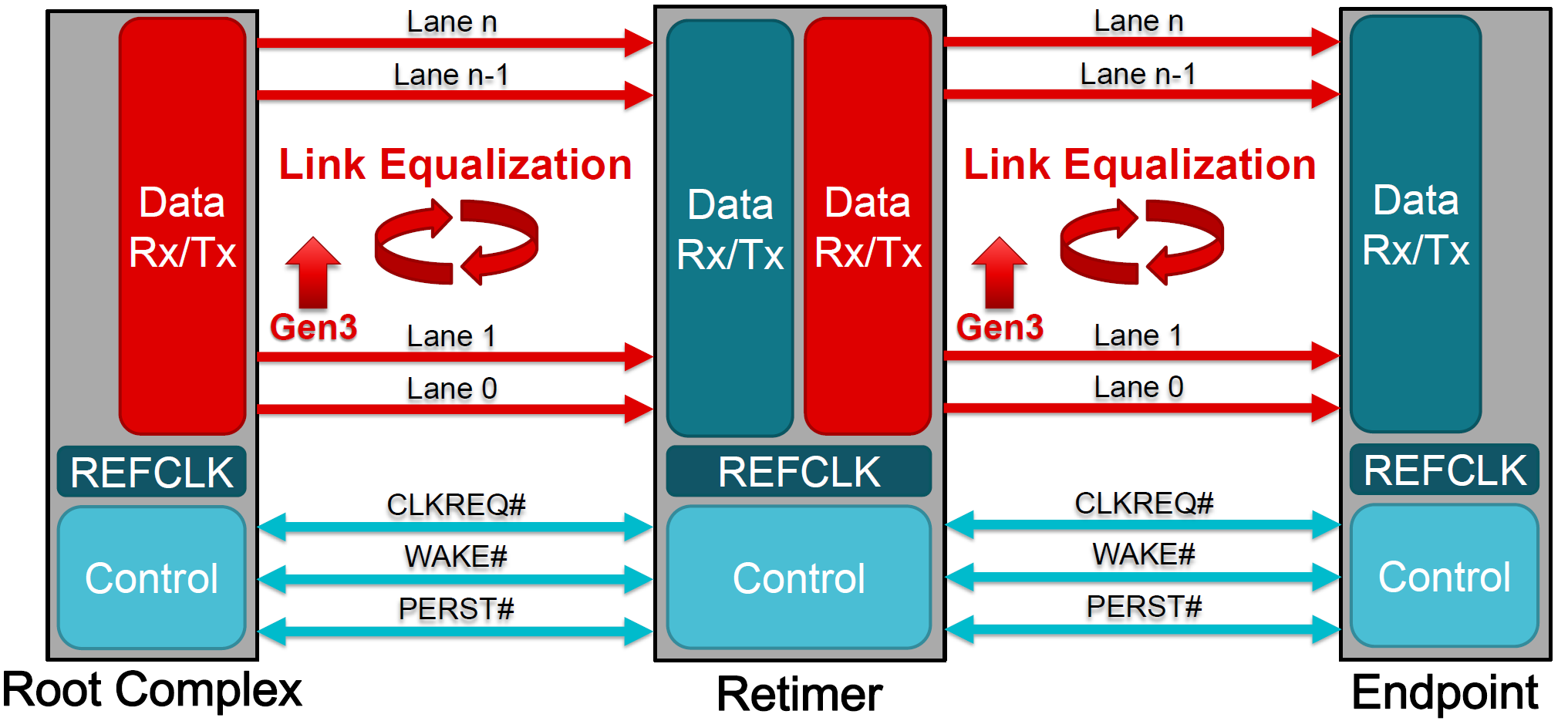

Phase 0 is the first phase of link equalization. This phase starts when the downstream port sends desired transmitter preset values for each lane to the upstream device. Shortly after receiving the downstream port's request, the upstream port increases the data rate of the link to Gen 3 data rate and begins transmitting training sequences back to the downstream port using the desired presets. Link equalization moves to phase 1 once the connection with Gen 3 is achieved. Figure 6-2 shows the phase 0 of link equalization from Gen 1 to Gen 3 connection with red arrows of each lane pointing the downstream device to represent the upstream device transmitting desired preset values. The link's data rate increases to the data rate of PCIe Gen 3.

Figure 6-2 Link Equalization Phase 0 and

1

Figure 6-2 Link Equalization Phase 0 and

1In phase 1, identical training sequences are sent repeatedly to ensure the correct presets are received, despite the possibility of poor link quality. This is done in order to optimize the link enough to be able to exchange training sequences and complete the remaining link equalization phases for fine tuning. Link equalization moves to phase 2 when the link has achieved a link with a bit error rate (BER) of less than 10-4.