SNLA415 August 2022 DS160PT801

6 Link Equalization

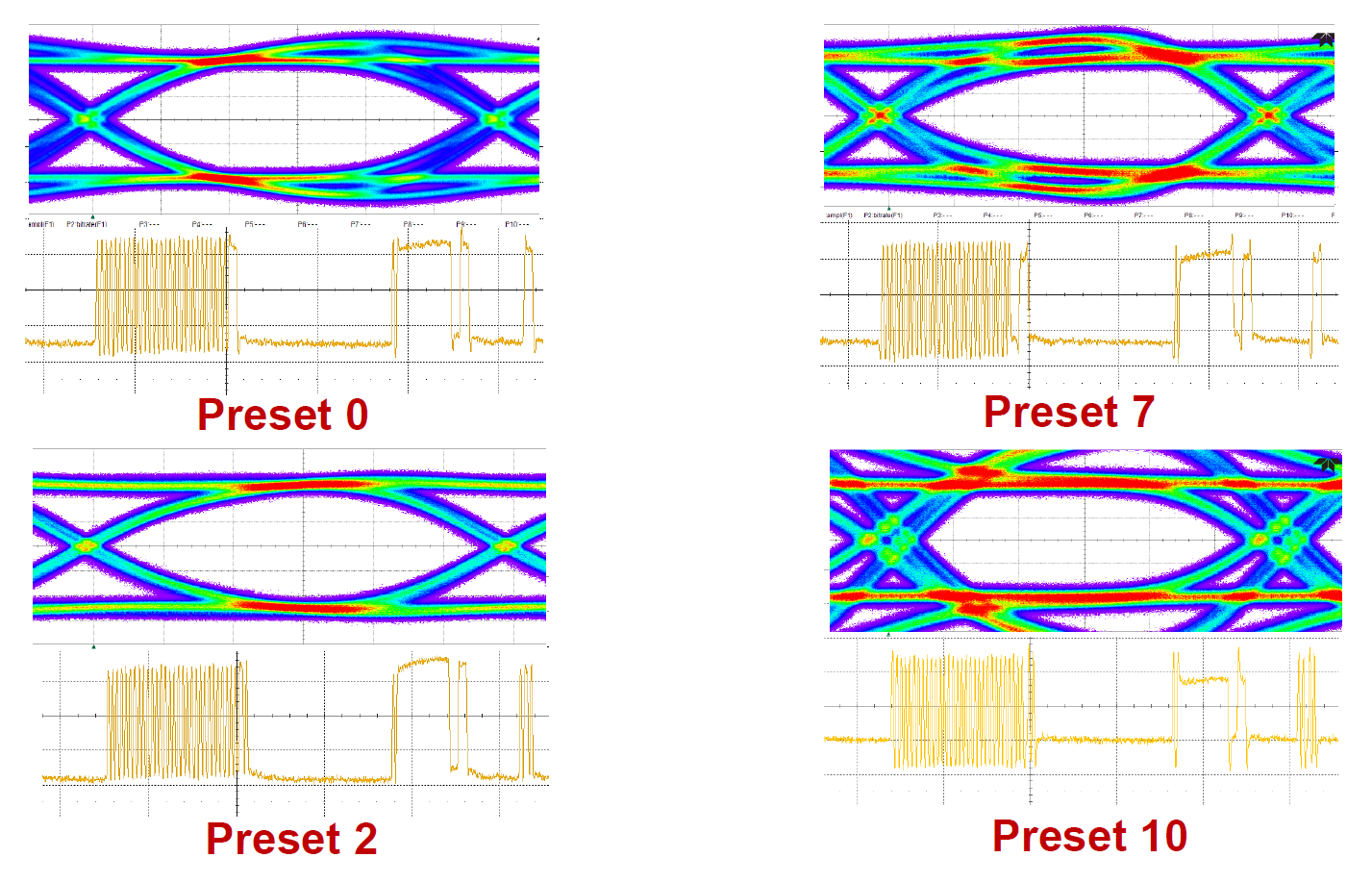

After link training, all PCIe devices may go through additional link equalization processes to establish stable connection among the devices. Link equalization is a link optimization process that modifies the characteristics of the transmitted data waveform for each part so that it results in the most stable PCIe link at a higher data rate. It happens when all devices in PCIe link can support data rates of PCIe Gen 3 or higher. Link equalization may happen multiple times since PCIe connection has to optimize the connection at every generation of PCIe above Gen 3. For example, if all PCIe devices are Gen 5, there will be three link equalization processes: first to Gen 3, from Gen 3 to Gen 4, and from Gen 4 to Gen 5. Link equalization is achieved by using the preset values defined in PCIe specification. Preset values are configurations that can modify the characteristics of the transmitted data wave form. Figure 6-1 shows select preset values in waveform and eye diagram.

Figure 6-1 Link Equalization Preset

Values and Signals

Figure 6-1 Link Equalization Preset

Values and SignalsFor Gen 3 and Gen 4, there are 11 presets numbered from 0 to 10 that may be used, each with its own unique signal characteristics. The preset values for each port are negotiated through link equalization until the ideal preset is chosen via phases 0, 1, 2, and 3 for all link equalization processes.