SNLA415 August 2022 DS160PT801

2 History

PCIe is based on the predecessor PCI. The PCI bus existed on many motherboards in the 1990s, along with a few other expansion bus technologies. Motherboard expansion bus standards are designed for communication between the CPU and devices plugged into the motherboard's expansion slots. Initially, all expansion bus standard used a parallel bus, which means that data is sent and received over multiple channels.

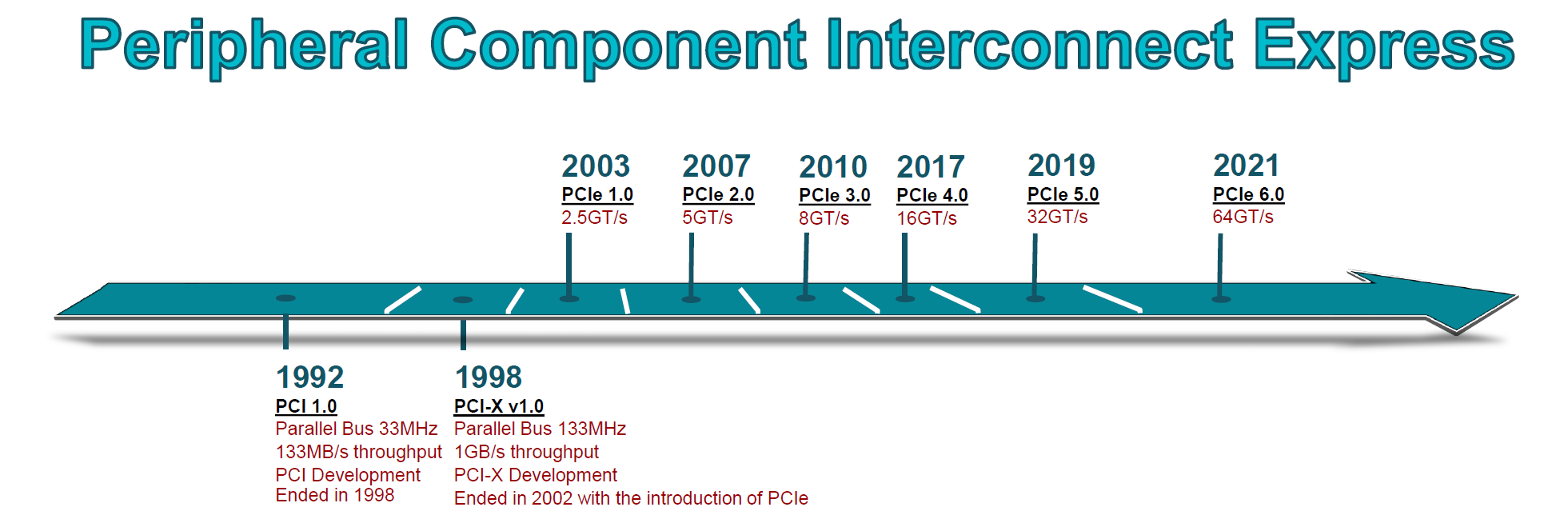

At the time of its introduction in 2003, the PCIe serial bus standard was meant to replace these older parallel buses to enable a higher data rate and to simplify system design. In 2003, the PCIe standard was defined by the PCI-SIG organization. Since then, the PCIe standard has iteratively improved over time to accommodate the latest bandwidth needs of modern computers. In 2021, the PCIe 6.0 specification was introduced, enabling 64 GT/s, or 64 Gbps per link. One unique feature of the PCIe standard is the ability to increase the number of lanes from 1 to 32 lanes to increase its throughput, a feature inspired by its parallel bus predecessor. A PCIe 6.0 link that is 16 lanes wide would have a data rate of 128 GB/s, which is extremely fast by today's standards. Figure 2-1 shows the timeline of PCIe development and its data rate over the generations along with its predecessors' data rate.

Using the parallel bus feature, PCIe can establish link with other PCIe devices in link width of 1, 2, 4, 8, 16, and even 32 lanes as defined in the PCIe standard. Different link width allows PCIe devices to transmit more data by using more lanes or vice versa as needed by the machine. Having different link width also allows you to bifurcate, or split, the lanes that are used for the device. In doing so, you can attach multiple PCIe devices onto one PCIe slot.

Since the development, PCIe standard has been used for variety of form factors. One of the more popular form factors besides CEM (Card Electromechanical) is M.2. M.2 is a replacement interface for mSATA and Mini PCIe and is mainly used for SSD connection to the CPU.

Figure 2-1 Timeline of PCIe

Interface

Figure 2-1 Timeline of PCIe

Interface