ZHCSD93A january 2015 – december 2020 UCC28700-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Applications and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Transformer Parameter Verification

- 8.2.2.2 Output Capacitance

- 8.2.2.3 VDD Capacitance, CDD

- 8.2.2.4 VDD Start-Up Resistance, RSTR

- 8.2.2.5 VS Resistor Divider, Line Compensation, and Cable Compensation

- 8.2.2.6 Input Bulk Capacitance and Minimum Bulk Voltage

- 8.2.2.7 Transformer Turns Ratio, Inductance, Primary-Peak Current

- 8.2.2.8 Standby Power Estimate

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

-

11Device and Documentation Support

- 11.1

Device Support

- 11.1.1

Device Nomenclature

- 11.1.1.1 Capacitance Terms in Farads

- 11.1.1.2 Duty Cycle Terms

- 11.1.1.3 Frequency Terms in Hertz

- 11.1.1.4 Current Terms in Amperes

- 11.1.1.5 Current and Voltage Scaling Terms

- 11.1.1.6 Transformer Terms

- 11.1.1.7 Power Terms in Watts

- 11.1.1.8 Resistance Terms in Ω

- 11.1.1.9 Timing Terms in Seconds

- 11.1.1.10 Voltage Terms in Volts

- 11.1.1.11 AC Voltage Terms in VRMS

- 11.1.1.12 Efficiency Terms

- 11.1.1

Device Nomenclature

- 11.2 Documentation Support

- 11.3 Trademarks

- 11.1

Device Support

- Mechanical, Packaging, and Orderable Information

7.4.1 Primary-Side Voltage Regulation

Figure 7-1 shows a simplified flyback convertor with the main voltage regulation blocks of the device shown. The power train operation is the same as any DCM flyback circuit but accurate output voltage and current sensing is the key to primary-side control.

Figure 7-1 Simplified Flyback Convertor (with the main voltage regulation blocks)

Figure 7-1 Simplified Flyback Convertor (with the main voltage regulation blocks)In primary-side control, the output voltage is sensed on the auxiliary winding during the transfer of transformer energy to the secondary. As shown in Figure 7-2 it is clear there is a down slope representing a decreasing total rectifier VF and resistance voltage drop (ISRS) as the secondary current decreases to zero. To achieve an accurate representation of the secondary output voltage on the auxiliary winding, the discriminator reliably blocks the leakage inductance reset and ringing, continuously samples the auxiliary voltage during the down slope after the ringing is diminished, and captures the error signal at the time the secondary winding reaches zero current. The internal reference on VS is 4.05 V; the resistor divider is selected as outlined in the VS pin description.

Figure 7-2 Auxiliary Winding Voltage

Figure 7-2 Auxiliary Winding VoltageThe UCC28700-Q1 VS signal sampler includes signal discrimination methods to ensure an accurate sample of the output voltage from the auxiliary winding. There are however some details of the auxiliary winding signal to ensure reliable operation, specifically the reset time of the leakage inductance and the duration of any subsequent leakage inductance ring. Refer to Figure 7-3 for a detailed illustration of waveform criteria to ensure a reliable sample on the VS pin. The first detail to examine is the duration of the leakage inductance reset pedestal, TLK_RESET in Figure 7-3. Because this can mimic the waveform of the secondary current decay, followed by a sharp downslope, it is important to keep the leakage reset time less than 500 ns for IPRI minimum, and less than 1.5 µs for IPRI maximum. The second detail is the amplitude of ringing on the VAUX waveform following TLK_RESET. The peak-to-peak voltage at the VS pin should be less than approximately 100 mVp-p at least 200 ns before the end of the demagnetization time, tDM. If there is a concern with excessive ringing, it usually occurs during light or no-load conditions, when tDM is at the minimum. The tolerable ripple on VS is scaled up to the auxiliary winding voltage by RS1 and RS2, and is equal to 100 mV x (RS1 + RS2) / RS2.

Figure 7-3 Auxiliary Waveform Details

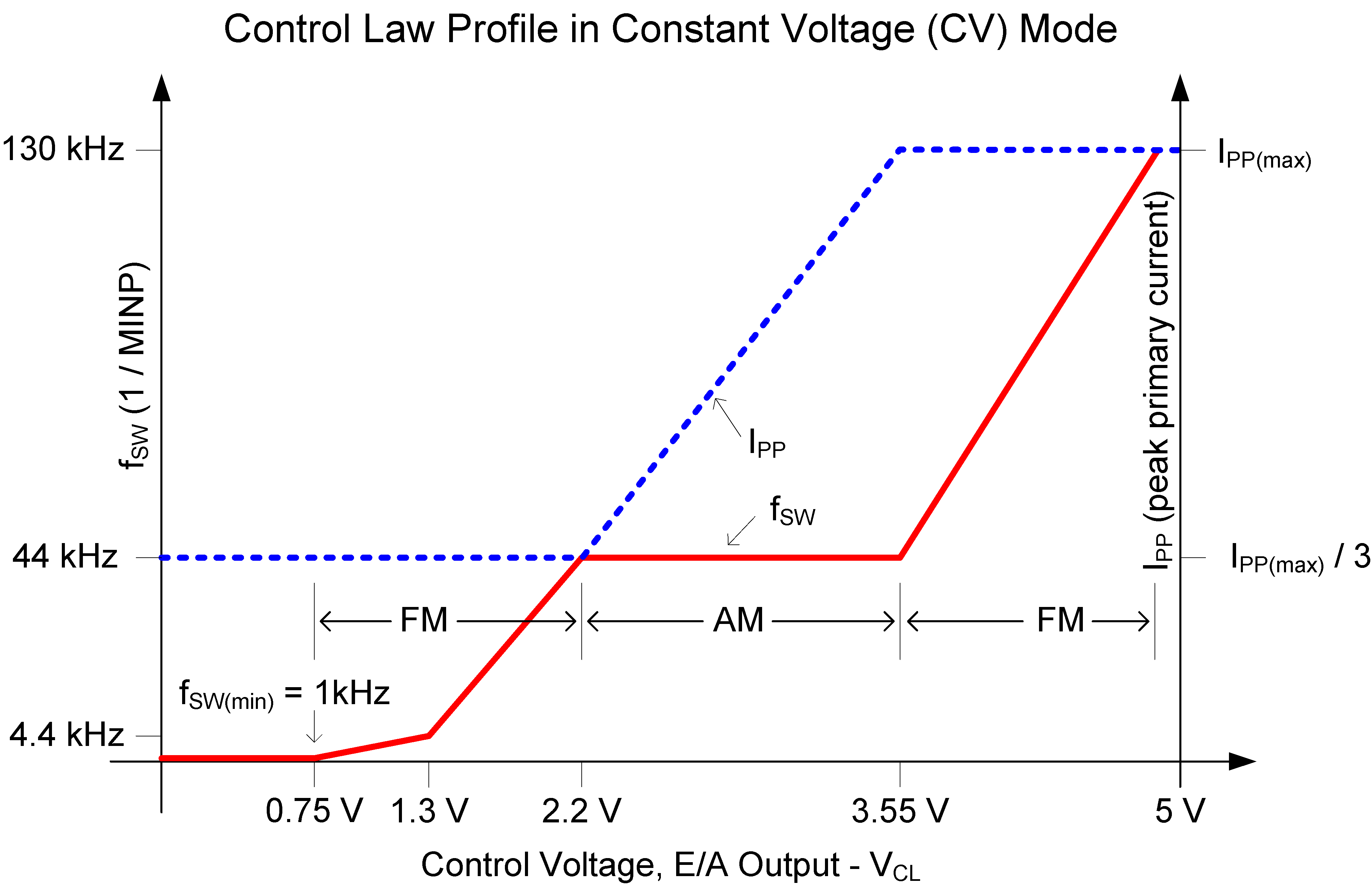

Figure 7-3 Auxiliary Waveform DetailsDuring voltage regulation, the controller operates in frequency modulation mode and amplitude modulation mode as illustrated in Figure 7-4 below. The internal operating frequency limits of the device are 130 kHz maximum and 1 kHz minimum. The transformer primary inductance and primary peak current chosen sets the maximum operating frequency of the converter. The output preload resistor and efficiency at low power determines the converter minimum operating frequency. There is no stability compensation required for the UCC28700-Q1 controller.

Figure 7-4 Frequency and Amplitude Modulation Modes (during voltage regulation)

Figure 7-4 Frequency and Amplitude Modulation Modes (during voltage regulation)