ZHCSYB8 May 2025 LMK1C1102A , LMK1C1103A , LMK1C1104A , LMK1C1106A , LMK1C1108A

PRODUCTION DATA

5 引脚配置和功能

- DQF (WSON) 封装相当于其他供应商的 DFN 封装。

图 5-3 LMK1C1103A,8 引脚 PW TSSOP 封装(顶视图)

图 5-3 LMK1C1103A,8 引脚 PW TSSOP 封装(顶视图) 图 5-5 LMK1C1104A,8 引脚 PW TSSOP 封装(顶视图)

图 5-5 LMK1C1104A,8 引脚 PW TSSOP 封装(顶视图) 图 5-7 LMK1C1108A,16 引脚 PW TSSOP 封装(顶视图)

图 5-7 LMK1C1108A,16 引脚 PW TSSOP 封装(顶视图) 图 5-2 LMK1C1102A,8 引脚 PW TSSOP 封装(顶视图)

图 5-2 LMK1C1102A,8 引脚 PW TSSOP 封装(顶视图)

- DQF (WSON) 封装相当于其他供应商的 DFN 封装。

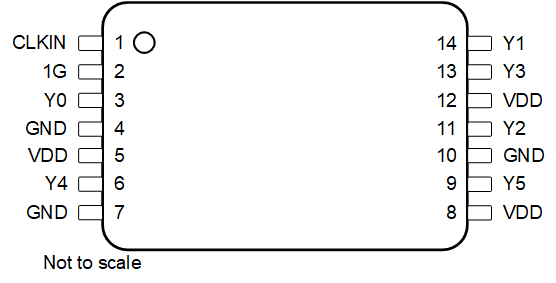

图 5-6 LMK1C1106A,14 引脚 PW TSSOP 封装(顶视图)

图 5-6 LMK1C1106A,14 引脚 PW TSSOP 封装(顶视图)表 5-1 引脚功能

| 引脚 | 类型 | 说明 | |||||

|---|---|---|---|---|---|---|---|

| 名称 | LMK1C 1102A |

LMK1C 1103A |

LMK1C 1104A |

LMK1C 1106A |

LMK1C 1108A |

||

| LVCMOS 时钟输入 | |||||||

| CLKIN | 1 | 1 | 1 | 1 | 1 | 输入 | 单端时钟输入,具有连接至 GND 的内部 300kΩ(典型值)下拉电阻。通常连接到单端时钟输入。 |

| 时钟输出使能 | |||||||

| 1G | 2 | 2 | 2 | 2 | 2 | 输入 | 全局输出使能,内部 300kΩ(典型值)下拉电阻至 GND。通常使用外部上拉电阻器连接到 VDD。 高电平:输出启用 低电平:输出禁用 |

| LVCMOS 时钟输出 | |||||||

| Y0 | 3 | 3 | 3 | 3 | 3 | 输出 | LVCMOS 输出。通常连接到接收器。未使用的输出可以保持悬空状态。 |

| Y1 | 8 | 8 | 8 | 14 | 16 | ||

| Y2 | — | 5 | 5 | 11 | 13 | ||

| Y3 | — | — | 7 | 13 | 15 | ||

| Y4 | — | — | — | 6 | 6 | ||

| Y5 | — | — | — | 9 | 11 | ||

| Y6 | — | — | — | — | 8 | ||

| Y7 | — | — | — | — | 9 | ||

| 电源电压 | |||||||

| VDD | 6 | 6 | 6 | 5 | 5 | 电源 | 电源端子。通常连接到 3.3V、2.5V 或 1.8V 电源。VDD 引脚通常连接到该引脚附近的外部 0.1μF 电容器。 |

| 8 | 10 | ||||||

| 12 | 14 | ||||||

| 接地 | |||||||

| GND | 4 | 4 | 4 | 4 | 4 | GND | 电源接地。 |

| 7 | 7 | ||||||

| 10 | 12 | ||||||