ZHCSL09C April 2020 – December 2020 LM7480-Q1

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

-

10Applications and Implementation

- 10.1 Application Information

- 10.2 Typical 12-V Reverse Battery Protection Application

- 10.3 200-V Unsuppressed Load Dump Protection Application

- 10.4 Do's and Don'ts

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

10.2.2.1 Input Transient Protection: ISO 7637-2 Pulse 1

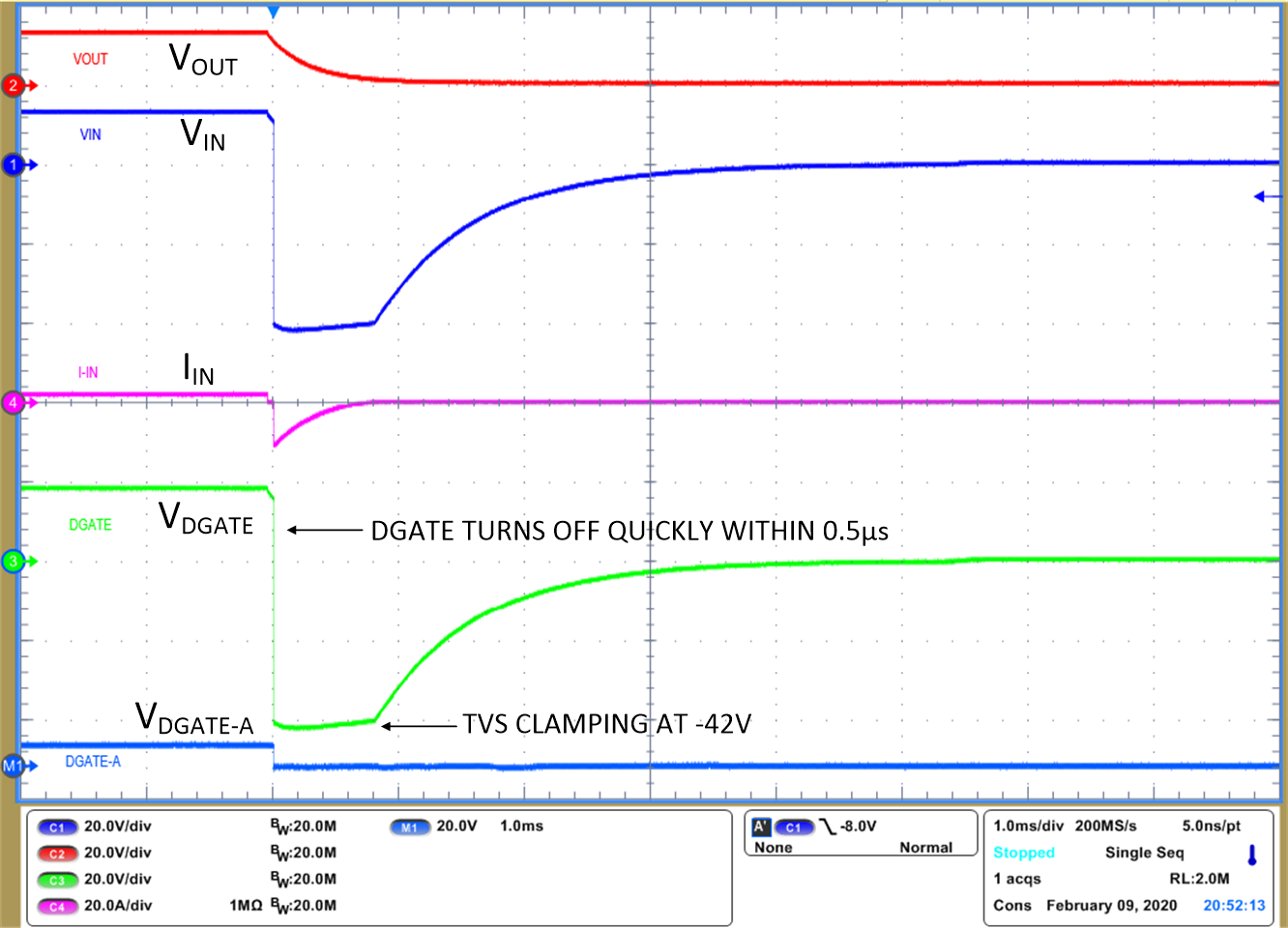

ISO 7637-2 Pulse 1 specifies negative transient immunity of electronic modules connected in parallel with an inductive load when the battery is disconnected. A typical pulse 1 specified in ISO 7637-2 starts with battery disconnection where supply voltage collapses to 0 V followed by –150 V 2 ms applied with a source impedance of 10 Ω at a slew rate of 1 µs on the supply input. LM7480x-Q1 blocks reverse current and prevents the output voltage from swinging negative, protecting the rest of the electronic circuits from damage due to negative transient voltage. MOSFET Q1 is quickly turned off within 0.5 µs by fast reverse comparator of LM7480x-Q1. A single bi-directional TVS is required at the input to clamp the negative transient pulse within the operating maximum voltage across cathode to anode of 85 V and does not violate the MOSFET Q1 drain-source breakdown voltage rating.

ISO 7637-2 Pulse 1 performance of LM74800-Q1 is shown in Figure 10-2.

Figure 10-2 ISO 7637-2 Pulse 1

Figure 10-2 ISO 7637-2 Pulse 1