ZHCSBP4C September 2013 – December 2016 DRV8303

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Current Shunt Amplifier Characteristics

- 6.7 SPI Characteristics (Slave Mode Only)

- 6.8 Gate Timing and Protection Switching Characteristics

- 6.9 Typical Characteristics

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

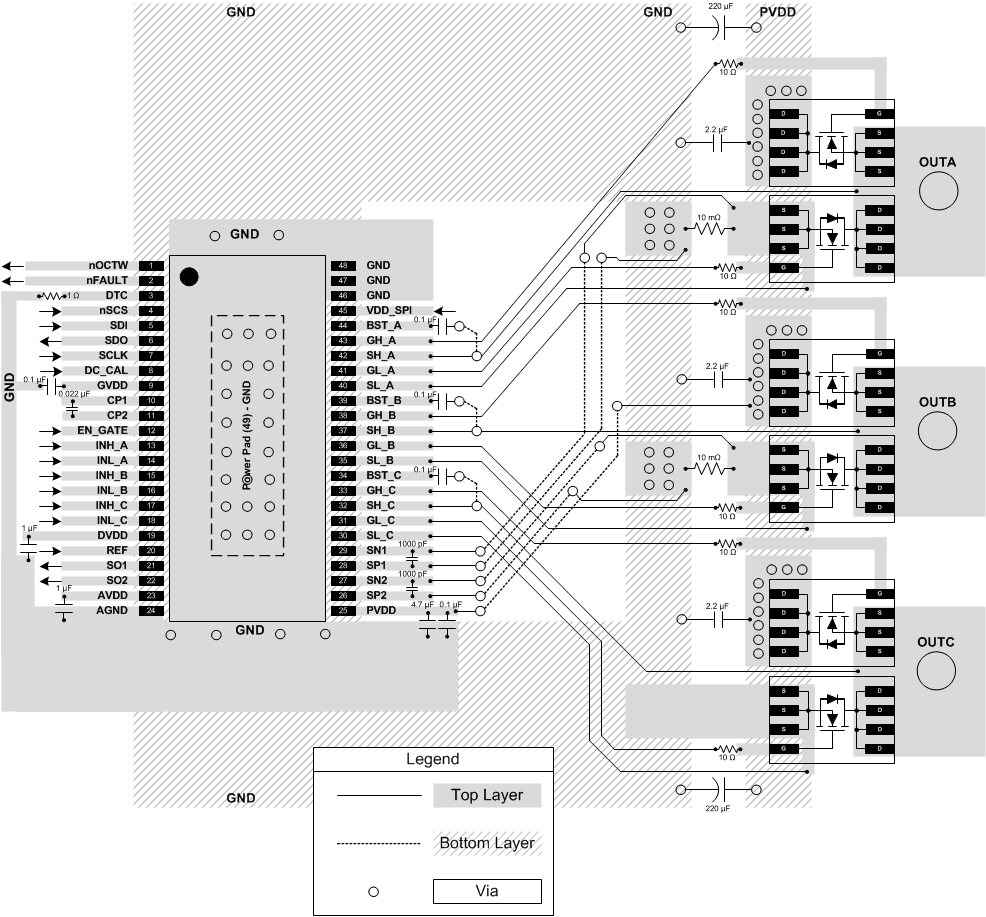

10 Layout

10.1 Layout Guidelines

Use these layout recommendations when designing a PCB for the DRV8303.

- The DRV8303 makes an electrical connection to GND through the PowerPAD. Always check to ensure that the PowerPAD has been properly soldered (see PowerPAD™ Thermally Enhanced Package).

- PVDD bypass capacitors should be placed close to their corresponding pins with a low impedance path to device GND (PowerPAD).

- GVDD bypass capacitor should be placed close its corresponding pin with a low impedance path to device GND (PowerPAD).

- AVDD and DVDD bypass capacitors should be placed close to their corresponding pins with a low impedance path to the AGND pin. It is preferable to make this connection on the same layer.

- AGND should be tied to device GND (PowerPAD) through a low impedance trace/copper fill.

- Add stitching vias to reduce the impedance of the GND path from the top to bottom side.

- Try to clear the space around and underneath the DRV8303 to allow for better heat spreading from the PowerPAD.

10.2 Layout Example

Figure 13. Layout Recommendation

Figure 13. Layout Recommendation