ZHCSAO1D January 2013 – August 2016 CSD97374Q4M

8.4 Normalized Curves

The normalized curves in the CSD97374Q4M data sheet give engineers guidance on the power loss and SOA adjustments based on their application specific needs. These curves show how the power loss and SOA boundaries will adjust for a given set of systems conditions. The primary Y-axis is the normalized change in power loss and the secondary Y-axis is the change is system temperature required in order to comply with the SOA curve. The change in power loss is a multiplier for the power loss curve and the change in temperature is subtracted from the SOA curve.

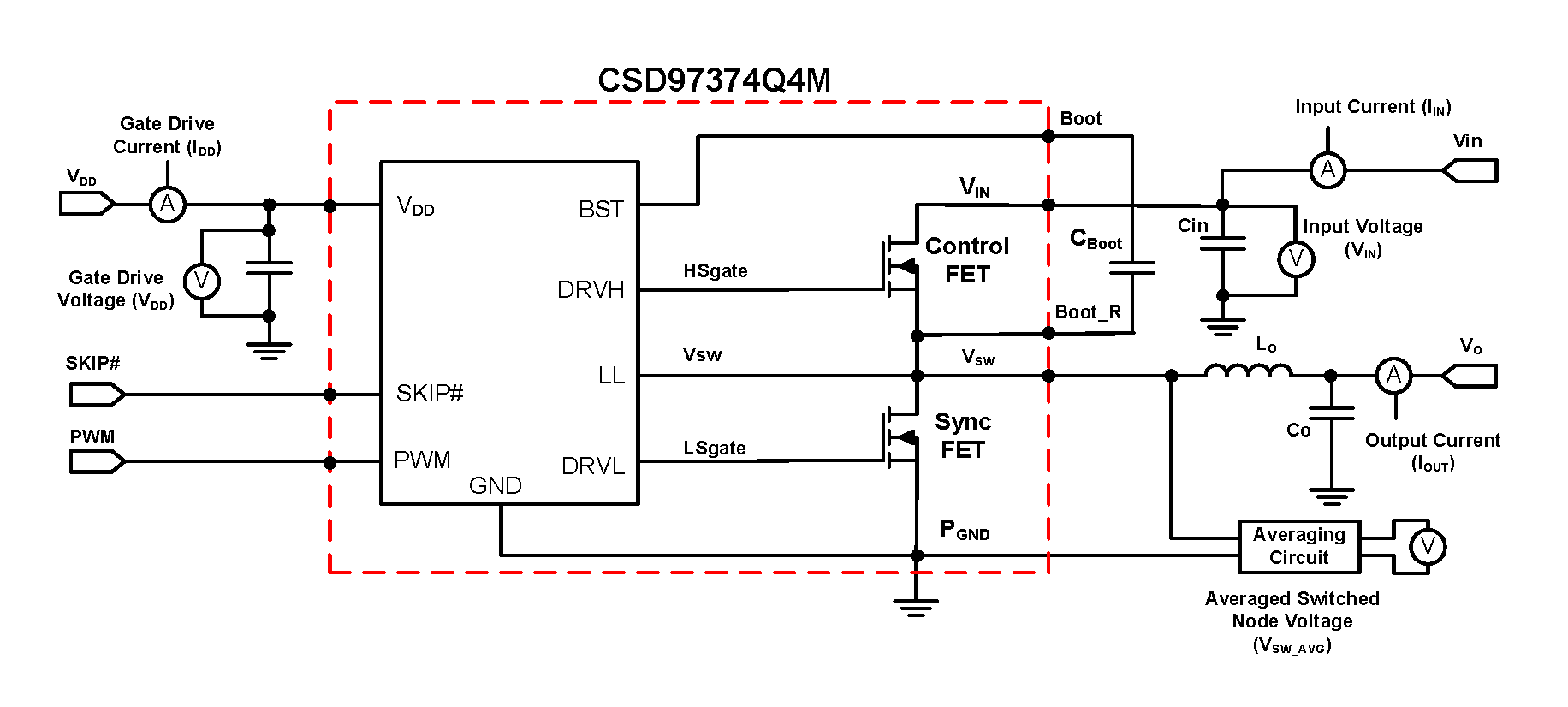

Figure 14. Power Loss Test Circuit

Figure 14. Power Loss Test Circuit