ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.3.1 信号连接

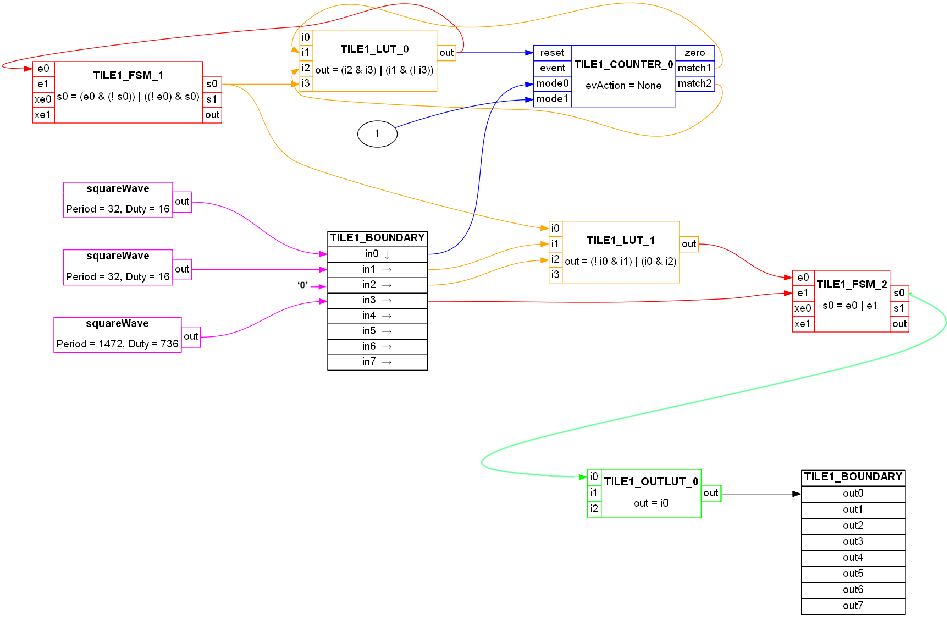

C2000Ware 随附的工具之一是图形化逻辑块查看器,它可以显示给定 CLB 设计的所有 CLB 组件以及相关的信号互连。该工具可以快速检查所有预期的 CLB 组件是否已启用并正确连接。除了标识活动的组件和连接之外,该查看器还显示 FSM 和 LUT 组件内部的输入信号、输出信号和逻辑方程。请注意,该查看器的当前版本仅限于显示 CLB 逻辑块的内部信息(它当前不支持逻辑块的输入信号选择和逻辑块输出的外设信号多路复用器分配)。图 4-9 显示了该查看器的屏幕截图,该屏幕截图适用于示例 16 的 CLB 逻辑块 1。查看逻辑块 1 的组件,您可以看到预期的两个 FSM 块、两个 LUT 块和一个计数器,其中 FSM 和 LUT 块显示了输入和输出之间的内部逻辑方程。仔细查看这些逻辑方程,您将看到它们与 图 4-8 的原理图相匹配。同样明显的是,有四个输入信号进入逻辑块 1,一个输出信号从逻辑块 1 中退出。

图 4-9 CLB 示例 16 – 以可视化方式显示逻辑块 1 内部的信号连接

图 4-9 CLB 示例 16 – 以可视化方式显示逻辑块 1 内部的信号连接