ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.1 CLB 示例 16 – 将两个 EPWM 输出与来自 CPREG 寄存器的信号组合在一起

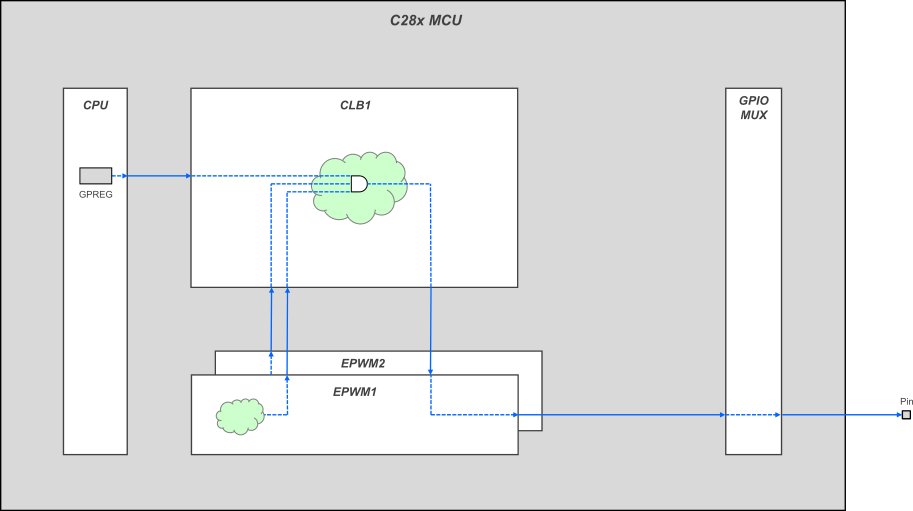

在该示例中,自定义逻辑应用于两个 EPWM 块的输出以及 GPREG 寄存器中的一个位,产生的输出信号通过 GPIO 引脚退出器件。图 3-1 显示了该示例的功能原理图。查看信号,可以看到 EPWM1 和 EPWM2 模块的输出与 CLB1 内的 GPREG 位结合在一起,并将结果反馈到 EPWM1 中,以转发至 GPIO 多路复用器,随后再转发至标准 EPWM1 输出通常使用的器件引脚。请注意,CLB1 的输出不会直接路由到 GPIO 多路复用器,而是会在输出级返回到 EPWM1 模块,从输出级开始,芯片的其余部分像对待正常 EPWM1 输出一样处理它。另请注意,进入 CLB1 的 EPWM 信号是在输出级之前从其各自的 EPWM 模块中提取的,但它们被重定向到 CLB1,而不是被发送到 GPIO 多路复用器。该实例在 FPGA 和 C2000 MCU 都实际运行后,两者的结果是一致的,请参阅Topic Link Label4。

图 3-1 CLB 示例 16 – 合并两个 EPWM 输出和一个来自 GPREG 寄存器的信号

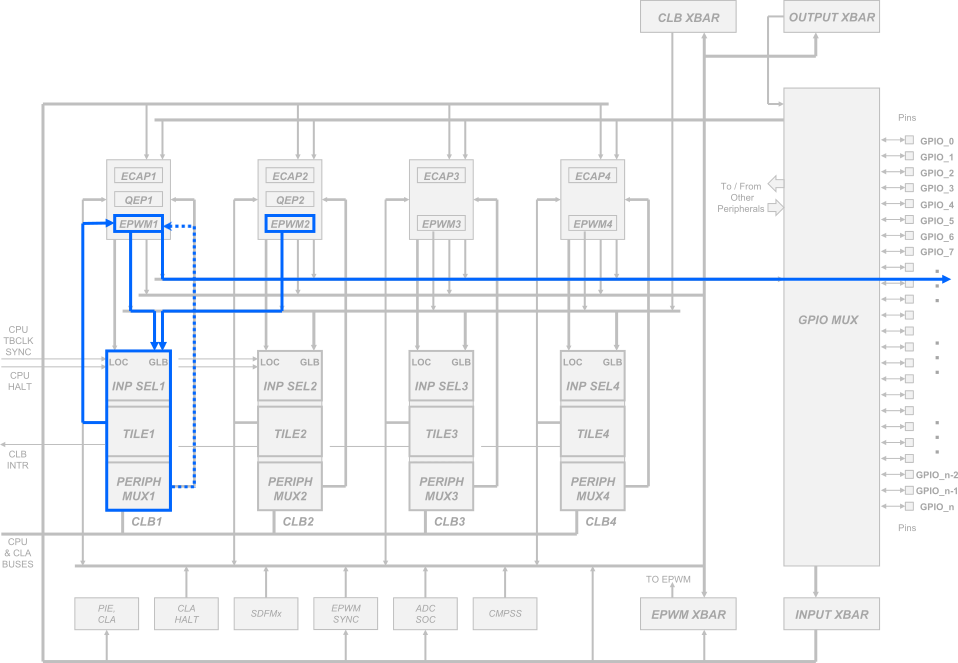

图 3-1 CLB 示例 16 – 合并两个 EPWM 输出和一个来自 GPREG 寄存器的信号图 3-2 通过器件级视图显示了相同的示例,以在 C2000 器件 I/O 部分的暗灰色背景下突出显示活动块和产生的数据传输。此处同样显示,通过使用全局信号总线将生成的 EPWM1A 和 EPWM2A 信号转移到 CLB1 中。请注意,EPWM1B、EPWM2A 和 EPWM2B 信号从相应的 EPMW 模块直接进入 GPIO 多路复用器。在 CLB1 内部应用了自定义逻辑之后,产生的信号通过 CLB1 输出总线反馈到 EPWM1 的最后一级。在返回到 EPWM1 模块内部之后,该输出信号立即退出,与正常 EPWM1A 输出一样转发到 GPIO 多路复用器。它从此处通过正常分配给 EPWM1A 的引脚退出芯片。

图 3-2 示例 16 中的信号流 – 器件视图

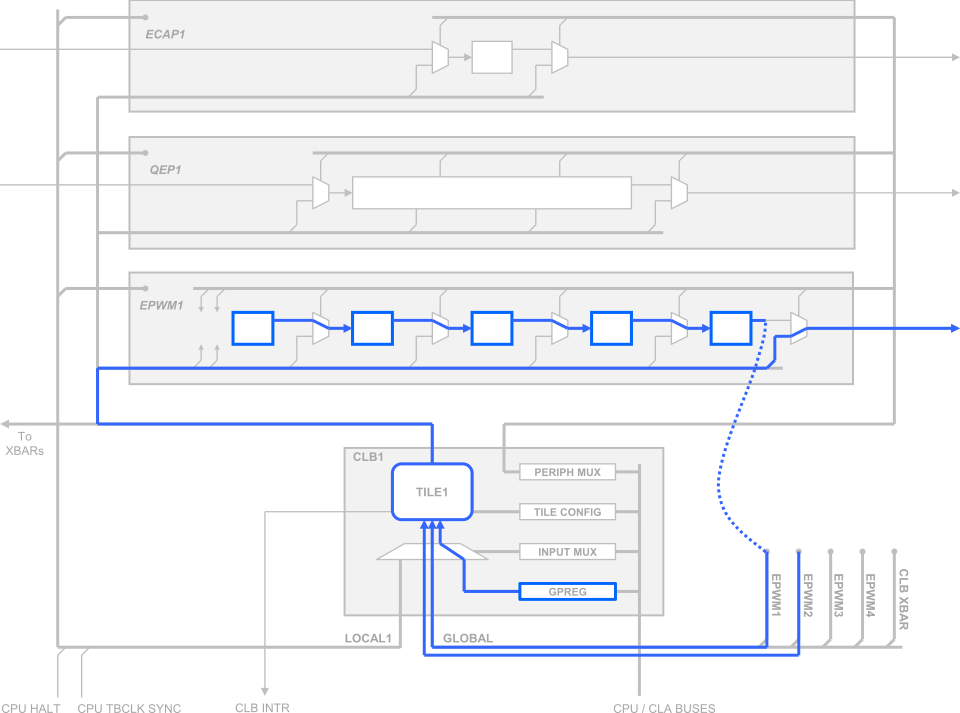

图 3-2 示例 16 中的信号流 – 器件视图图 3-3 通过 CLB1 连接的透镜提供了该示例的信号流详细信息。除了显示将 CLB1 与本地控制外设相连接的输入和输出之外,该视图还提供了 CLB1、EPWM1、QEP1 和 ECAP1 的内部详细信息及其内部的数据流。在进一步讨论之前,请注意,控制外设已在其内部嵌入了一组多路复用器,这些多路复用器允许来自 CLB1 本地输出总线的替代信号在预选的级注入到外设中(按照 CLB1 外设信号多路复用器控制的指示)。另请注意,可以在方便的位置从控制外设中提取信号,然后通过全局和本地 1 总线将其传送到 CLB1。

现在已做好准备,可以开始跟踪该示例的信号。首先,在 EPWM1A 信号即将离开 EPWM1 模块并进入全局信号总线之前,对该信号进行拦截。EPWM2A 信号也适用同样的操作。全局信号总线将这两个 EPWM 信号重新路由至 CLB1,其中的逻辑块 1 输入多路复用器选择这两个信号进入 TILE1。输入多路复用器还将 GPREG 寄存器中的一个位转发至逻辑块 1。这 3 个位一起进入 CLB1 的逻辑块 1,而连接到逻辑块 1 的 8 位输入总线的其余 5 个位未使用。在逻辑块 1 内部,将预定义的逻辑应用于 3 个输入,以产生一个输出信号(有八个可能的输出),并将其放置在 CLB1 输出信号总线上,该信号在此总线上返回到 EPMM1 模块。

返回到内部之后,输出信号由 EPWM1 模块最后一级后面的外设信号多路复用器进行选择,以退出 EPWM1 并开始向 GPIO 多路复用器传输,然后放置在分配给正常 EPWM1A 输出的引脚上。请注意,在此阶段,芯片的其余部分不知道也不关心从控制外设发出的信号是原始输出、CLB 修改的输出还是 CLB 产生的与原始外设无关的全新输出。这项强大的功能使 C2000 用户能够轻松地修改外设或创建新外设,而不必依赖外部 CPLD 或 FPGA,同时始终使用现有的芯片资源向/从新外设/修改的外设传递信号。

提醒一下,该示例(以及后面的示例)中的信号路径已由控制输入多路复用器选择器、逻辑块 1 配置和外设信号多路复用器的 CLB1 配置寄存器确定。输入多路复用器选择器和外设信号多路复用器控制信号由应用软件通过功能调用进行设置,而逻辑块 1 配置由 SysConfig 工具进行定义(生成代码,以响应用户与 SysConfig 图形用户界面的交互来设置逻辑块配置寄存器)。

图 3-3 示例 16 中的信号流 – CLB1 连接

图 3-3 示例 16 中的信号流 – CLB1 连接